# COM-5401SOFT Tri-Mode 10/100/1000 Ethernet MAC VHDL SOURCE CODE OVERVIEW

#### Overview

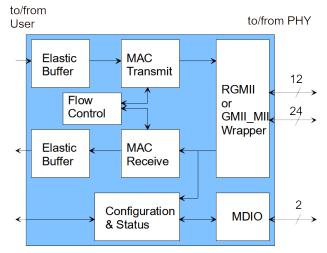

The COM-5401SOFT is a generic tri-mode Ethernet MAC core (including the VHDL source code) designed to support full- or half-duplex Gigabit throughput on low-cost FPGAs.

The component's very efficient implementation makes it suitable for multiple instantiations within a small FPGA. For example, it is instantiated four times (for a 4 Gbits/s combined throughput) in a small Spartan-6 XC6SLX16.

Key features include:

- Compliance with the IEEE 802.3-2008 specification.

- Configurable half-duplex/full-duplex operation.

- Address filter to reject undesirable received packets.

- Automatic

- Preamble generation and removal

- 32-bit CRC generation and checking.

- Packet re-transmission in case of collision (when half-duplex).

- Payload padding and pad removal for very short frames.

#### Keywords

Tri-mode, Ethernet MAC, 10/100/1000, MAC core, RGMII, GMII, VHDL, FPGA, GbE, Microchip KSZ9021/9031, Ethernet PHY, Ethernet transceiver.

### Block Diagram

### Target Hardware

The code is written in generic VHDL so that it can be ported to a variety of FPGAs. The code was developed and tested on a Xilinx Artix7 FPGAs.

It can be easily ported to any Xilinx Kintex7, Virtex-6, Virtex-5, Spartan-6 FPGAs and other FPGAs capable of running at 125 MHz.

Please note that the target FPGA must be capable of creating a 2ns delay on the RGMII transmit and receive clocks.

#### **Device Utilization Summary**

| Device: Xilinx Spartan-6 –2 speed |      |      |  |  |  |  |  |  |

|-----------------------------------|------|------|--|--|--|--|--|--|

| RGMII GMII/MI                     |      |      |  |  |  |  |  |  |

| Slice Registers                   | 726  | 738  |  |  |  |  |  |  |

| LUTs                              | 1023 | 1077 |  |  |  |  |  |  |

| Block RAM/FIFO                    | 3    | 3    |  |  |  |  |  |  |

| DSP48A1s                          | 0    | 0    |  |  |  |  |  |  |

| GCLKs                             | 2    | 3    |  |  |  |  |  |  |

| DCMs/PLLs                         | 0    | 0    |  |  |  |  |  |  |

|                                   | 0    |      |  |  |  |  |  |  |

Maximum user clk frequency: 153 MHz

| Device: Xilinx Kintex7 –3 speed |      |      |  |  |  |  |  |  |  |

|---------------------------------|------|------|--|--|--|--|--|--|--|

| RGMII GMII/M                    |      |      |  |  |  |  |  |  |  |

| Slice Registers                 | 714  | 731  |  |  |  |  |  |  |  |

| LUTs                            | 1003 | 1000 |  |  |  |  |  |  |  |

| Block RAM/FIFO                  | 2    | 2    |  |  |  |  |  |  |  |

| DSP48A1s                        | 0    | 0    |  |  |  |  |  |  |  |

| GCLKs                           | 2    | 3    |  |  |  |  |  |  |  |

| DCMs/PLLs                       | 0    | 0    |  |  |  |  |  |  |  |

Maximum user clk frequency: 315 MHz

#### Interfaces

| C_RESET                            | CLOCKS                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                             | MII_TX_CLK<br>GMII_TX_CLK<br>GMII_MII_TXD(7:0)                                                                                                                                                                                                                                                                                                                                                                                                               | $\stackrel{\leftarrow}{\rightarrow}$                                                                                                                                                                                                                                                                                  |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_DATA_VALID<br>TX_EOF            | ΤΧ DATA                                                                                                                                                                                                                                                                                                                                       | gmii<br>Mii<br>Phy                                                                                                                                                                                          | GMII_MII_TX_EN<br>GMII_MII_TX_ER<br>GMII_MII_CRS<br>GMII_MII_COL                                                                                                                                                                                                                                                                                                                                                                                             | $\uparrow \downarrow \downarrow \downarrow$                                                                                                                                                                                                                                                                           |

| RX_DATA_VÁLID<br>RX_SOF<br>RX_EOF  | RX DATA                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                             | GMII_MII_RXD(7:0)<br>GMII_MII_RX_DV<br>GMII_MII_RX_ER                                                                                                                                                                                                                                                                                                                                                                                                        | `↓<br>↓<br>↓                                                                                                                                                                                                                                                                                                          |

| TX_CONFIG(15:0)<br>RX_CONFIG(15:0) | MAC<br>CONFIG                                                                                                                                                                                                                                                                                                                                 | RGMII<br>PHY                                                                                                                                                                                                | RGMII_TXC<br>RGMII_TXD(3:0)<br>RGMII_TX_CTL<br>RGMII_RXC<br>RGMII_RXD(3:0)<br>RGMII_RX_CTL                                                                                                                                                                                                                                                                                                                                                                   | $\uparrow \uparrow \uparrow \downarrow \downarrow \downarrow \downarrow$                                                                                                                                                                                                                                              |

| RESET                              | PHY<br>CONFIG                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                             | JS                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                       |

| STATUS<br>D_STATUS                 | PHY<br>STATUS                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                             | MCLK<br>MDIO                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\leftrightarrow$                                                                                                                                                                                                                                                                                                     |

|                                    | ERFACE<br>C_RESET<br>TX_DATA(7:0)<br>TX_DATA_VALID<br>TX_EOF<br>TX_CTS<br>RX_DATA_VALID<br>RX_DATA_VALID<br>RX_SOF<br>RX_CONFIG(15:0)<br>RX_CONFIG(15:0)<br>RX_CONFIG(15:0)<br>ADDR(47:0)<br>CONFIG_CHANGE<br>RESET<br>D(1:0)<br>EX<br>MODE(1:0)<br>EX<br>MODE(1:0)<br>SKEW(15:0)<br>STATUS<br>D_STATUS<br>D_STATUS<br>EX_STATUS<br>EX_STATUS | ERFACEC_RESETCLOCKSTX_DATA(7:0)TX DATATX_EOFTX DATATX_CTSTX DATARX_DATA_VALIDRX DATARX_OATA_VALIDRX DATARX_SOFRX DATARX_CONFIG(15:0)MACRADDR(47:0)PHYCONFIG_CHANGEPHYD(1:0)PHYERSETPHYD(1:0)STATUSSTATUSPHY | ERFACE     CLOCKS       C_RESET     CLOCKS       TX_DATA(7:0)     TX_DATA_VALID       TX_EOF     TX_DATA       TX_CTS     TX_DATA       RX_DATA(7:0)     RX_DATA       RX_DATA_VALID     RX_DATA       RX_SOF     RX_DATA       RX_CONFIG(15:0)     MAC       RX_CONFIG(15:0)     MAC       CONFIG_CONFIG(15:0)     MAC       CONFIG_CHANGE     PHY       CONFIG_CHANGE     PHY       CONFIG_CHANGE     PHY       SKEW(15:0)     STATUS       STATUS     PHY | ERFACEINTERFACEC_RESETCLOCKSMII_TX_CLKTX_DATA(7:0)TX_DATA_VALIDGMIITX_CTSTX DATAGMIIRX_DATA_VALIDTX DATAGMIIRX_DATA_VALIDTX DATAGMIIRX_SOFRX DATAGMII_MII_TX_ERRX_CONFIG(15:0)MACGMII_MII_RX_CLKRX_CONFIG(15:0)MACRGMII_MII_RX_CTLCONFIG_CHANGEPHYCONFIGCONFIG_CHANGEPHYCONFIGSTATUSPHYCONTROLSTATUSPHYMCLKMIDOSTATUS |

#### **User Interface**

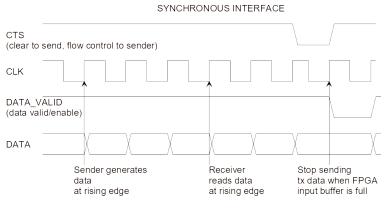

This interface comprises three primary signal groups: transmit data, receive data and monitoring & control. All signals are clock synchronous with a user-selected clock CLK (it does not have to be the same as the 125/25/2.5 MHz PHY clocks).

For maximum throughput, 16Kb elastic buffers are included in both tx/rx directions at the user interface. This allows the MAC engine to multitask, sending a complete packet to the PHY while accepting subsequent packet data from the user.

When space is available in the tx elastic buffer, the user can send an Ethernet frame as illustrated below:

| Destination Address           | 6Bytes                           |

|-------------------------------|----------------------------------|

| Source Address                | 6Bytes                           |

| Length / Type                 | 2Bytes                           |

| MAC Client Data               | 46-1500Bytes<br>(pad is added to |

| Pad                           | reach minimum<br>size)           |

| Frame Check Sequence<br>(CRC) | 4Bytes                           |

The software inserts the pad and frame check sequence (CRC) fields automatically unless disabled by the user.

The software then encapsulates the tx frame into an Ethernet Packet by adding a preamble, start of frame delimiter and extension as needed.

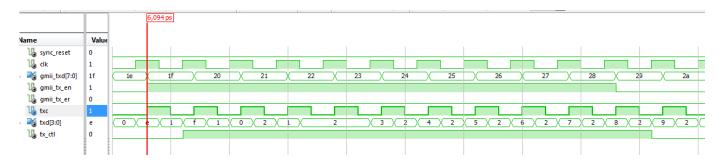

#### User Interface timing

#### PHY Interface

The COM-5401SOFT interfaces with an external 10/100/1000 Ethernet PHY through one of several standard Media Independent Interfaces. The interface type is user-selected with the MII\_SEL generic signal prior to VHDL synthesis.

#### $MII_SEL = '0'$

- RGMII for 10/100/1000 Mbps

#### $MII\_SEL = '1'$

- MII for 10/100 Mbps as per 802.3 clause 22

- GMII for 1000 Mbps as per 802.3 clause 35

In parallel, the external PHY is managed via a twowire standard MDIO interface. The GMII/MII interface is fairly generic. It should work with most PHYs with only very minor code changes. In particular, the delay between clock and data may need to be adjusted for the target hardware through the constants RXC\_DELAY and TXC\_DELAY in the *GMII\_MII\_WRAPPER.vhd* component, in order to avoid glitches.

The RGMII interface is also fairly generic, except for the clock/data/control timing adjustment written for the Microchip KSZ9021/9031 PHY. Changes in the extended control registers to adjust the clock skew are expected when using a PHY from another vendor (see *PHY\_CONFIG.vhd*).

Additional PHY-specific configuration options are also defined at the time of power-up/reset. See the "Strapping options" section.

#### Configuration

#### **Pre-synthesis configuration parameters**

The following configuration parameters are set prior to synthesis in the generic section of the *COM5401.vhd* component declaration.

| Generic              | Description                    |

|----------------------|--------------------------------|

| MII interface type   | MII_SEL.                       |

|                      | Select the MII interface type: |

|                      |                                |

|                      | 0 = RGMII                      |

|                      | 1 = GMII/MII                   |

| PHY IC address       | 5-bit PHY IC address           |

|                      | PHY_ADDR                       |

| User clock frequency | The user-supplied CLK          |

|                      | serves as time reference for   |

|                      | internal timers/delays.        |

|                      | Declare the frequency in       |

|                      | MHz (120 for 120 MHz, etc)     |

|                      | CLK_FREQUENCY                  |

#### **Run-time configuration parameters**

The user can set and modify the following controls at run-time. All controls are synchronous with the user-supplied global CLK.

| CLK.                       |                                                                                                                                                                                             |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAC transmit configuration | Description                                                                                                                                                                                 |

| Auto-padding               | 1 = Automatic padding of short<br>frames. Requires that auto-CRC<br>insertion be enabled too.<br>0 = Skip padding. User is<br>responsible for adding padding<br>to meet the minimum 60 byte |

|                        | frame size.                                             |

|------------------------|---------------------------------------------------------|

|                        |                                                         |

|                        | MAC_TX_CONFIG (0)                                       |

| Auto-CRC               | 1 = Automatic appending of 32-                          |

|                        | bit CRC at the end of the frame                         |

|                        | 0 = Skip CRC insertion. User is                         |

|                        | responsible for including the                           |

|                        | frame check sequence.                                   |

|                        | MAC_TX_CONFIG(1)                                        |

| MAC receive            | Description                                             |

| configuration          |                                                         |

| MAC address            | This network node 48-bit MAC                            |

|                        | address. The receiver checks                            |

|                        | incoming packets for a match                            |

|                        | between the destination address                         |

|                        | field and this MAC address.                             |

|                        | The user is responsible for                             |

|                        | selecting a unique 'hardware'                           |

|                        | address for each instantiation.                         |

|                        | Natural bit order: enter                                |

|                        | x0123456789ab for the MAC                               |

|                        | address 01:23:45:67:89:ab                               |

| Promiscuous mode       | 1 = all valid frames are                                |

|                        | accepted, regardless of their                           |

|                        | destination address.                                    |

|                        | 0 = destination addresses are                           |

|                        | checked.                                                |

|                        | MAC_RX_CONFIG(0)                                        |

| Allow rx broadcast     | 0 = filter out packets with the                         |

| packets                | broadcast destination address                           |

|                        | FF:FF:FF:FF:FF.                                         |

|                        | 1 = accepts broadcast packets.                          |

|                        | MAC_RX_CONFIG(1)                                        |

| Allow rx multi-cast    | 0 = filter out packets with the                         |

| packets                | multicast bit set in the                                |

|                        | destination address.                                    |

|                        | 1 = accepts multicast packets.                          |

|                        | MAC_RX_CONFIG(2)                                        |

| Filter out padding and | 1 = filter out the pad and CRC                          |

| CRC fields             | fields.                                                 |

|                        | 0 = pass along the entire                               |

|                        | Ethernet frame including pad                            |

|                        | and CRC fields.                                         |

|                        | MAC_RX_CONFIG(1)                                        |

| PHY configuration      | Description                                             |

| Speed                  | Select autonegotiation or force                         |

|                        | the PHY to operate at a specific                        |

|                        | speed.                                                  |

|                        | 00 = force 10 Mbps                                      |

|                        | 01 = force 100 Mbps                                     |

|                        | 10 6 1000 10                                            |

|                        | 10 = force 1000 Mbps<br>11 = auto-negotiation (default) |

| Half/Full duplex | Half-duplex is a safe           |

|------------------|---------------------------------|

|                  | configuration which can be used |

|                  | with older networking           |

|                  | equipment. Full duplex results  |

|                  | in higher throughput but may be |

|                  | incompatible with unswitched    |

|                  | hubs.                           |

|                  | 0 = half-duplex                 |

|                  | 1 = full duplex.                |

| PHY test mode    | 00 = normal mode (default)      |

|                  | 01 = loopback mode (at the      |

|                  | phy)                            |

|                  | 10 = remote loopback            |

|                  | 11 = led test mode              |

| PHY reset        | 1 = PHY software reset,         |

|                  | 0 = no reset                    |

| PHY power down   | 1 = power down enabled          |

|                  | 0 = disabled                    |

|                  |                                 |

To enact any PHY configuration, a pulse must be sent to PHY\_CONFIG\_CHANGE.

#### **MAC Receive Packets Check**

The MAC receive section performs the following checks on the incoming packets:

- frame size  $\geq 64$  bytes

- frame size <= 1518 bytes

- frame length field is consistent with actual received frame size

- destination address matches the userspecified MAC address, or

- destination address is a broadcast or multicast address

- Frame check sequence (CRC) is verified.

When an incoming packet passes all above checks, it is forwarded to the user via a 16Kb rx elastic buffer.

### Exclusions

This software does not support the following 802.3-2008 options:

- Packet bursting (half duplex mode 1000Mbps only) Section 4.2.3.2.7

### Software Licensing

The COM-5401SOFT is supplied under the following key licensing terms:

- 1. A nonexclusive, nontransferable license to use the VHDL source code internally, and

- 2. An unlimited, royalty-free, nonexclusive transferable license to make and use products incorporating the licensed materials, solely in bitstream format, on a worldwide basis.

The complete VHDL/IP Software License Agreement can be downloaded from http://www.comblock.com/download/softwarelicense.pdf

#### Reference documents

[1] IEEE Std. 802.3<sup>™</sup>-2008 Relevant clauses:

- Clause 3: MAC frame and packet specifications

- Clause 4: Media Access Control

- Clause 22: Reconciliation Sublayer and Media Independent Interface (MII)

- Clause 35: Reconciliation Sublayer and Gigabit Media Independent Interface (GMII)

[2] Reduced Gigabit Media Independent Interface (RGMII) 4/1/2002 Version 2.0

[3] Microchip KSZ9031RNX specifications, "Gigabit Ethernet Transceiver with RGMII Support", 2016

[4] ComBlock COM-1800 FPGA (XC7A100T) + ARM + DDR3 SODIMM socket + GbE LAN development platform www.comblock.com/com1800.html

### **Configuration Management**

The current software revision is 8.

| Directory    | Contents                                                                              |

|--------------|---------------------------------------------------------------------------------------|

| /            | Project files for various Xilinx Vivado versions.                                     |

| /doc         | Specifications, user manual, implementation documents                                 |

| /src         | .vhd source code, .ucf constraint<br>files, .pkg packages.<br>One component per file. |

| /sim         | Test benches                                                                          |

| /bin         | .ngc, .bit, .mcs configuration files                                                  |

| /use_example | use example, .ngc for Spartan-6 and instantiation template                            |

### VHDL development environment

The VHDL software was developed using the following development environment: Xilinx Vivado 2020.2 for compilation and VHDL simulation tools.

Older versions of Vivado can be used by importing the *com-5401\_ISE14.xise* Xilinx ISE project.

#### Ready-to-use Hardware

The binary component (.ngc) is freely available for use on the following Comblock hardware module:

COM-1800 FPGA + ARM + DDR2 + NAND + USB2 development platform

See the following code templates:

https://comblock.com/download/com1800template %20003b.7z

The hardware schematics are here:

https://comblock.com/download/com\_1800schemat ics.pdf

#### Xilinx-specific code

The VHDL source code is written in generic VHDL with few Xilinx primitives. No Xilinx CORE is used. The Xilinx primitives are:

- IBUF

- IBUFG

- BUFG (global clocks)

- IDDR2 (RGMII DDR input)

- ODDR2 (RGMII DDR output)

- IODELAY2 to delay the RGMII clocks

- RAM block: RAMB16\_S9\_S9

#### Synthesis

The *com5401.vhd* MAC can be synthesized as a black box to be included in large projects. To generate this "black box" .ngc file, the Xilinx Vivado synthesis properties must first be configured as follows:

- Xilinx Specific Options

- o Add I/O buffers: disabled

- Pack I/O registers in IOBs: No

The synthesis process then generates a .ngc output file.

When synthesizing the final project, synthesis should be configured with "Pack I/O registers in IOBs: yes" as it results in better timing.

### Top-Level VHDL hierarchy

- Inst\_RESET\_TIMER RESET\_TIMER Behavioral (Com5401.vhd)

Inst\_RESET\_TIMER RESET\_TIMER Behavioral (RESET\_TIMER.vhd)

Inst\_PHY\_CONFIG PHY\_CONFIG Behavioral (PHY\_CONFIG.vhd)

Inst\_MI\_MI MII\_MI Behavioral (MII\_MI.vhd)

Inst\_RGMII\_WRAPPER RGMII\_WRAPPER Behavioral (RGMII\_WRAPPER.vhd)

Inst\_RGMI\_MI\_MI MIL\_MI Behavioral (MII\_MI.vhd)

Inst\_RGMII\_WRAPPER GMII\_WRAPPER Behavioral (GMII\_MRAPPER.vhd)

Inst\_SISTIC LFSR11C behavior (LFSR11C.VHD)

Inst\_CRC32\_8B CRC32\_8B behavioral (crc32\_8b.vhd)

- RX\_CRC32\_8B CRC32\_8B behavioral (crc32\_8b.vhd)

The code is stored with one, and only one, component per file.

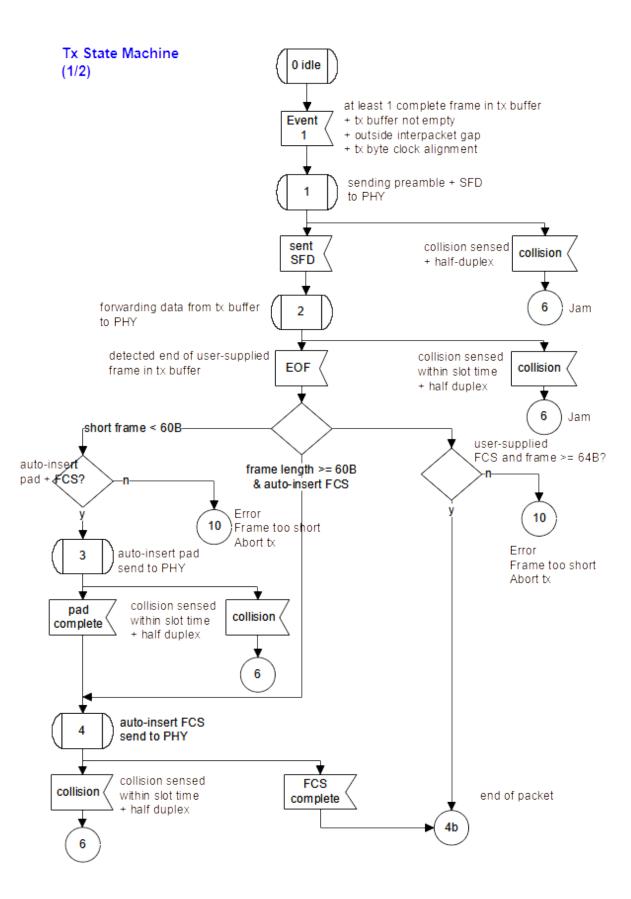

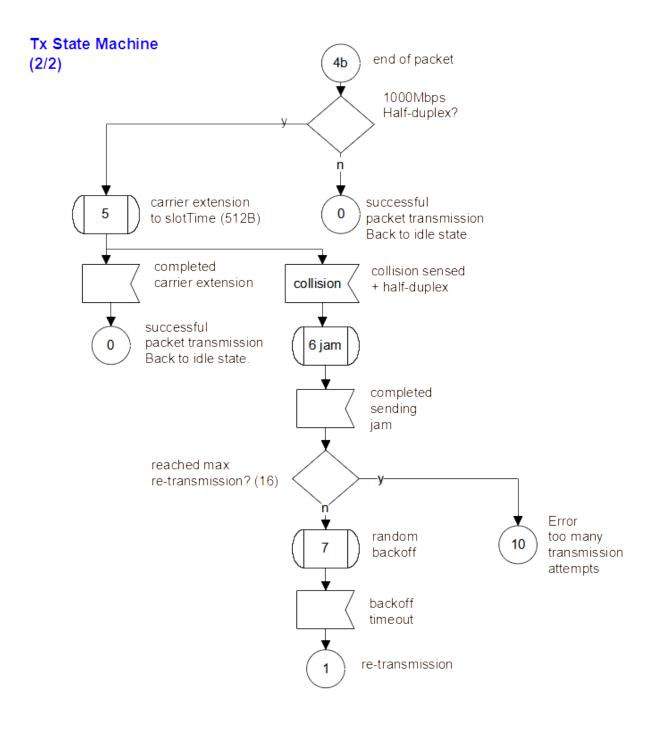

The root entity (highlighted above) is *COM5401.vhd*. It comprises the tx and rx elastic buffers, tx state machine and tx packet construction.

The root also includes the following components:

- The *PHY\_CONFIG.vhd* component to configure the PHY.

- The *RGMII\_WRAPPER.vhd* converts the natural PHY interface to the lower pin-count RGMII.

- The *GMII\_MII\_WRAPPER.vhd* converts the natural PHY interface to the standard GMII (1000 Mbps) or MII (10/100 Mbps) interface.

- The *CRC32\_8B.vhd*, instantiated twice, computes the CRC32 to be appended to tx packets and to check rx. The CRC32 computation is performed 8 data bits at a time.

### Clock / Timing

The software uses the following main clocks:

- A 125/25/2.5 MHz receive clock generated by the PHY. The speed depends on the recovered LAN signal. In the RGMII and GMII cases, the receive clock is looped back and used as transmit clock.

- In the MII case, the transmit clock is supplied by the PHY.

- A user-supplied interface clock (CLK) to read and write packets from/to the MAC. CLK frequency is independent of the PHY clock but should be high enough to support the expected data throughput.

# Quick Start

This section describes a few tips to quickly establish a working, albeit simple, baseline.

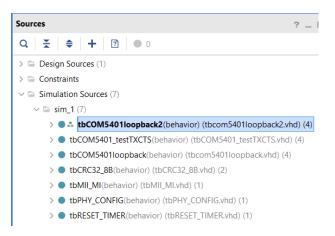

#### Quick start with VHDL simulation

Several testbenches located in the /sim directory can be used to validate the VHDL code. Some focus on detailed areas (CRC32, MDIO timing, PHY configuration), while others create stimulus to exercise the entire Ethernet MAC.

The easiest way to start is to use the Xilinx Vivado VHDL simulator.

Highlight one of the testbenches, set it as default and run the simulation.

For example, the *tbCOM5401loopback.vhd* testbench sends a 42-byte Ethernet frame to the RGMII PHY where it is looped back. This allows one to visualize the PHY interface signals, padding and CRC insertion by the MAC layer and the frame verification upon reception.

The SIMULATION constant (typically at the top level) should be set to '1' to enable configurations specific to the VHDL simulation, shorten long timers for example. These constants should revert to '0' prior to synthesis.

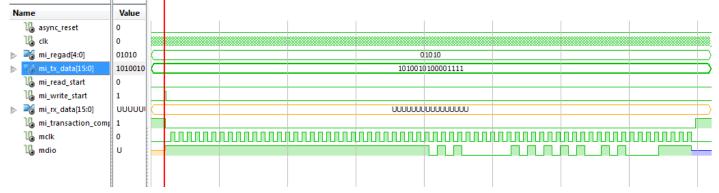

# MII Management Interface

The PHY is managed through a two-wire Management Data Input/Output (MDIO) interface. The MDIO is a synchronous serial link comprising two signals: a clock MCLK and a bi-directional data line MDIO. The MDIO timing diagram is specified by the IEEE 802.3 standard.

The component *MII\_MI.vhd* implements a read or write transaction, converting a 16-bit parallel register value and 5-bit register address to a serial stream and vice-versa.

A write transaction (sending 0xA50F to register address 10) is illustrated below:

The write sequence consists of

- (a) 32-bit preamble field (all ones)

- (b) "0101"

- (c) 5-bit PHY address, here fixed at 0

- (d) REG address MI\_REGAD[4:0]

- (e) "10"

- (f) 16-bit data field MI\_TX\_DATA[15:0]

A read transaction (receiving 0Xffff from register address 10) is shown below:

| 🕼 sync_reset         | 0     |            | <u> </u> |        |       |  |      |

|----------------------|-------|------------|----------|--------|-------|--|------|

| 🗓 cik                | 0     |            |          |        |       |  |      |

| 📷 mi_regad[4:0]      | 01010 |            |          |        | 01010 |  |      |

| 🏹 mi_tx_data[15:0]   | a50f  |            |          |        | a50f  |  |      |

| 🍓 mi_read_start      | 0     |            |          |        |       |  |      |

| 🍓 mi_write_start     | 0     |            |          |        |       |  |      |

| 16 mdio              | 1     |            |          |        |       |  |      |

| ni_rx_data[15:0]     | υυυυ  |            |          | ψυυυ   |       |  | fe00 |

| 🍓 mi_transaction_cor | 0     |            |          |        |       |  |      |

| 🗓 mclk               | 0     | <br>wwwwww | mmmm     | wwwwww | mm    |  |      |

|                      |       |            |          |        |       |  |      |

The read sequence consists of

- (g) a 32-bit preamble field (all ones) to the PHY

- (h) "0110" to the PHY

- (i) 5-bit PHY address, here fixed at 0 to the PHY

- (j) REG address MI\_REGAD[4:0] to the PHY

- (k) "Z"

- (1) "0" from the PHY

- (m) 16-bit data field MI\_RX\_DATA[15:0] from the PHY

The PHY generally sets a speed limit for the MDIO interface. For example, the Microchip KSZ9021/9031 PHY defines the typical MCLK frequency as 2.5 MHz. The *MII\_MI.vhd* component includes a constant (MCLK\_COUNTER\_DIV) to adjust the MCLK frequency by dividing the processing clock CLK. The designer

should adjust this constant prior to synthesis, depending on the specific MDIO timing requirements of the PHY IC.

## **PHY configuration**

The *PHY\_CONFIG.vhd* component encapsulates the PHY configuration as specified by the user. The configuration is triggered by a single pulse on the CONFIG\_CHANGE input.

The key configuration parameters are brought to the interface so that the user can change them dynamically at run time. Other, more arcane, parameters are fixed at the time of VHDL synthesis.

| Dynamic configuration parameter | Definition                                             |

|---------------------------------|--------------------------------------------------------|

| PHY_RESET                       | 1 = PHY software reset, $0 = no$ reset                 |

| SPEED                           | 00 = force 10 Mbps                                     |

|                                 | 01 = force 100 Mbps                                    |

|                                 | 10 = force 1000 Mbps                                   |

|                                 | 11 = auto-negotiation                                  |

| DUPLEX                          | 1 = full-duplex, $0 = $ half-duplex                    |

| TEST_MODE                       | 00 = normal mode                                       |

|                                 | 01 = loopback mode                                     |

|                                 | 10 = remote loopback                                   |

|                                 | 11 = led test mode                                     |

| POWER_DOWN                      | software power down mode. $1 = enabled, 0 = disabled.$ |

A CONFIG\_CHANGE pulse will trigger the state machine as shown below. The *PHY\_CONFIG.vhd* component subsequently writes to two PHY control registers at register addresses 0 and 17 respectively.

| 🏰 sync_reset                        | 0  |   |                  |   |    |   |    |   |   |

|-------------------------------------|----|---|------------------|---|----|---|----|---|---|

| 🗓 clk                               | 0  |   |                  |   |    |   |    |   |   |

| 埍 config_change                     | 1  |   |                  |   |    |   |    |   |   |

| · · · ·                             | 1  |   |                  |   |    |   |    |   |   |

|                                     | 11 |   |                  |   | 11 |   |    |   |   |

| · ·                                 | 1  |   |                  |   |    |   |    |   |   |

| ¥i test_mode[1:0]<br>Iug power_down | 00 |   |                  |   | 00 |   |    |   |   |

| 埍 power_down                        | 0  |   |                  |   |    |   |    |   |   |

| 🔓 mclk                              | 0  |   | .000000000000000 |   |    |   |    |   |   |

| ALC: N                              | U  |   |                  |   |    |   |    |   |   |

| ➡ mi_regad[4:0]<br>➡ state[3:0]     | 0  |   |                  | 0 | X  |   | 17 |   |   |

| 📷 state[3:0]                        | 0  | 0 |                  | 2 | Х  | 3 |    | X | 0 |

| 🌡 mi_write_start                    | 0  |   |                  |   |    |   |    |   |   |

|                                     |    |   |                  |   |    |   |    |   |   |

#### PHY strapping options configuration

Depending on the PHY integrated circuit, a few configuration options are set at the time of power-up or reset. For example, the Microchip KSZ9021/9031RN PHY uses general output pins (RX\_D, RX\_DV, etc) as temporary inputs during power-up or reset. These temporary inputs allow the FPGA to configure a few PHY options. The designer should therefore define pull-ups or pull-downs for these dual-function signals in the .ucf constraint file.

#### Example:

```

# strap-in configuration. Micrel KSZ9021RN

1

# advertise all capabilities: 10/100/1000

2

NET "RXD<3>" PULLUP ;

3

4 NET "RXD<2>" PULLUP ;

5 NET "RXD<1>" PULLUP ;

NET "RXD<0>" PULLUP ;

6

# enable 125 MHz clock reference to FPGA (at least for one PHY, not needed for all PHYs)

7

8 NET "RX CTL" PULLUP;

9

# dual LED mode

10 NET "CLK125 NDO" PULLDOWN;

This PHY address is 4

11

# PHYAD2

12

NET "RXC" PULLUP;

13 # repeat the code above for each PHY

```

The PHY may also impose a minimum reset duration at power up. For example, the Microchip KSZ9021/9031RN PHY requires a minimum 10ms reset duration at power up. The *RESET\_TIMER.vhd* component generates such a reset. Upon de-assertion of the RESET\_N signal, the PHY reads the strapping options as defined in the .ucf file. Following the reset, the PHY needs another 40ms to start. The *RESET\_TIMER.vhd* delays the PHY configuration until the PHY is up and running (as visible from the 125 MHz clock output from the PHY).

## **RGMII Interface**

The *RGMII\_WRAPPER.vhd* component translates the 6-pin receive PHY interface (DDR, 4-bit niblets) into a simpler (single clock edge, data-byte) interface. A symmetrical translation is performed on the transmit side, as illustrated below:

RGMII Transmit Side :

The *RGMII\_WRAPPER.vhd* component includes two delays to be configured prior to synthesis: constant RXC\_DELAY: integer range 0 to 255 := 32; -- adjust as needed. Here: 2ns constant TXC\_DELAY: integer range 0 to 255 := 32; -- adjust as needed. Here: 2ns

These delays offset the RXC and TXC synchronous clocks so as to avoid a race condition (and the possible resulting glitches) when reclocking the data with the associated clock at the receiving end. The recommended delay is between 1.5 and 2.0 ns [2]. When the clocks operate at 125 MHz, the IODELAY2 Xilinx primitive implements a delay by increments of 16ns/256 = 62.5ps. Thus, a configuration value of 32 results in a 2ns delay.

The *RGMII\_WRAPPER.vhd* component includes two methods for creating a 2ns offset between the receive clock RXC and the receive data. The baseline method is to set the delay in the extended control register 260 of the PHY. This method works well with Microchip KSZ9021/9031 PHY but may not be supported by other Manufacturers' PHYs. An alternative method using IODELAY2 in the FPGA is also coded but currently commented out.

#### GMII/MII Interface

The *GMII\_MII\_WRAPPER.vhd* component reformat signals exchanged between the FPGA and an external GMII/MII PHY.

The receive clock RX\_CLK is always supplied by the PHY to the FPGA. Its frequency (2.5,25 or 125 MHz) depends on the 10/100/1000 Mbps link speed negotiated by the PHY.

The transmit clock direction depends on the selected speed: The MII TX\_CLK is from the PHY to the FPGA, at speeds of 2.5 or 25 MHz (10/100 Mbps link) The GMII GTX\_CLK is a 125 MHz from the FPGA to the PHY (1000 Mbps link)

# MAC Tx State Machine

The tx state machine is described by the SDL flowchart below:

# MAC CRC32

All 802.11 frame include a 32-bit CRC (frame check sequence FCS). As part of the MAC layer processing, this software automatically appends the 32-bit CRC at transmission and verifies the CRC validity upon receiving a frame from the PHY. A single VHDL component *crc32\_8b.vhd* is used for both CRC32 generation and CRC check.

The algorithm is as follows:

- (a) The CRC32 field is set to x"FFFFFFF" at the start of frame.

- (b) Parallel implementation of the CRC32 takes one clock for each input byte.

- (c) The generator polynomial is

- $G(x) = x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1.$

- (d) The CRC is inverted prior to transmission. The transmission is least significant bit first.

- (e) Verification is done by feeding an entire frame (including the 32-bit CRC at the end) into the *crc32\_8b.vhd* component. When the frame is error free, the resulting CRC is the residual value 0xC704DD7B. This causes the CRC32\_VALID flag to go high.

The tb*crc32\_8b.vhd* testbench was created to verify proper operation. A null frame with 28 "00" bytes result in a 32-bit CRC x"6811f1fe". The CRC is inverted and flipped LSb first. Upon receiving this CRC at the end of a frame, the CRC check indicates a valid frame by raising the CRC32\_VALID flag.

| I sync_reset            | 0        |                                   |                |              |                |         |          |

|-------------------------|----------|-----------------------------------|----------------|--------------|----------------|---------|----------|

| 🎼 cik                   | 1        |                                   |                |              |                |         |          |

| 🏹 crc32_in[31:0]        | 6811f1fe |                                   | b5a1           | 6811f1fe     |                |         | 9b5cd    |

| ata_in[7:0]             | 00       |                                   |                |              |                | 00      |          |

| 🎼 sample_clk_ref        | 0        |                                   |                |              |                |         |          |

| 🎼 sample_clk_in         | 0        |                                   |                |              |                |         |          |

| 🍯 crc32_out[31:0]       | 6811f1fe | Xfbac7c3a X0e8f0c68 xb382c80a X32 | b5a1           | 6811f1fe     |                |         | 9b5cd    |

| 🔓 crc32_valid           | 0        |                                   |                |              |                |         |          |

| 😸 counter[9:0]          | 01f      | X 018 X 019 X 01a X               | 016 🗙 01c 🗙    | 01d 🗙 01e    | 01f            | 000     | 001      |

| 🝯 tx_data[7:0]          | 01       | 00                                | <u> </u>       | ee 🗙 Oe      | 01             | $\sim$  |          |

| 🐞 tx_data_lsbfirst[7:0] | 80       | 00                                | e9X            | 77 🗙 70      | 80             | $\sim$  |          |

| 🍯 crc32b_in[31:0]       | b6647d00 |                                   | b5a1 6811f1fe  | 006beX0eb664 | <b>6</b> 6647d | c704dd7 | 6 4710bb |

| 🍯 crc32b_out[31:0]      | b6647d00 | Xfbac7c3a X0e8f0c68 xb382c80a X32 | b5a1 16811f1fe | 006be 0eb664 | <b>b</b> 6647d | c704dd7 | 6 4710bb |

| 🔓 crc32b_valid          | 0        |                                   |                |              |                |         |          |

| 👃 clk_period            | 10000 ps |                                   |                |              |                | 10000 p | s        |

An alternate test bench tb*crc32\_8b\_alt.vhd* verifies the32-bit CRC for a packet collected over the LAN (assumed valid).

## ComBlock Compatibility List

| FPGA development platform                                                  |

|----------------------------------------------------------------------------|

| COM-1800 FPGA (XC7A100T) + ARM + DDR3 SODIMM socket + GbE LAN development  |

| platform                                                                   |

| Software                                                                   |

| COM-5402SOFT IP/TCP server/UDP for Gigabit Ethernet, VHDL Source / IP Core |

| COM-5403SOFT IP/TCP client/UDP for Gigabit Ethernet, VHDL Source / IP Core |

## **ComBlock Ordering Information**

COM-5401SOFT Tri-Mode 10/100/1000 Ethernet MAC, VHDL SOURCE CODE

ECCN: EAR99

MSS • 845 Quince Orchard Boulevard Ste N • Gaithersburg, Maryland 20878-1676 • U.S.A. Telephone: (240) 631-1111 E-mail: sales@comblock.com