# COM-1905 L/S-band continuous-mode PSK transceiver

# **Key Features**

- L/S-band modem to send and receive continuous streams over wireless, satellite or cable. (for burst-mode see <u>COM-1902</u>)

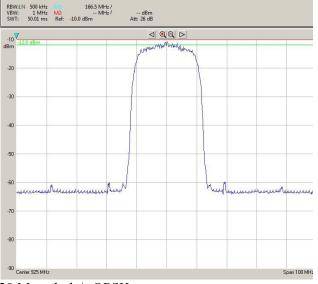

- BPSK/QPSK/OQPSK modulation. Programmable symbol rate, up to 40 MSymbols/s

- Nominal frequency of operation: 950 2175 MHz for direct connection to external LNB or BUC. Customization to other frequency bands is possible.

- Convolutional or Turbo code error correction.

- Built-in IP router with gigabit Ethernet LAN port

- Supply voltage: 18 36VDC with reverse voltage and surge protection. (5.6V min when not supplying external LNB)

- Frequency reference: internal TCXO or input for an external, higher-stability 10 MHz frequency reference.

- Built-in tools: PRBS-11 pseudo-random test sequence, BER tester, AWGN generator, internal loopback mode.

- Monitoring:

- Carrier frequency error

- o SNR

- o BER

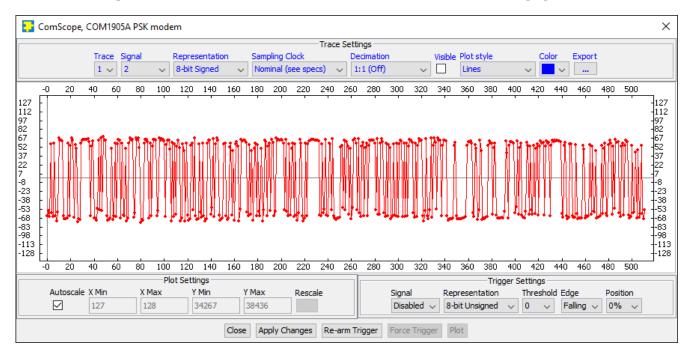

- ComScope –enabled: key internal signals can be captured in real-time and displayed on host computer.

For the latest data sheet, please refer to the **ComBlock** web site: <u>http://www.comblock.com/download/com1905.pdf</u>. These specifications are subject to change without notice.

For an up-to-date list of **ComBlock** modules, please refer to <u>http://www.comblock.com/product\_list.html</u>.

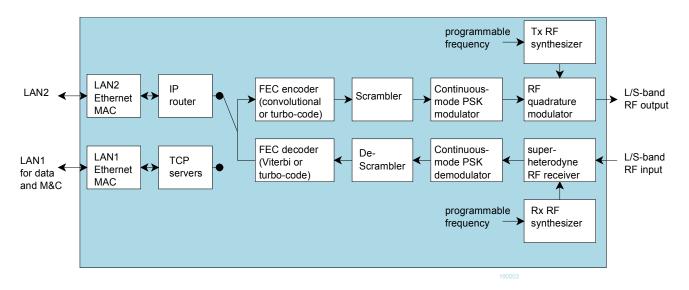

Functional Block Diagram

# Configuration (Basic)

The easiest way to configure the COM-1905 is to use the **ComBlock Control Center** software supplied with the module on CD. Please follow the few simple steps described in the user manual "<u>ccchelp.pdf</u>" document to install the ComBlock Control Center software "ComBlock\_Control\_Center\_windows\_rev.exe"

Connect the LAN cable between PC and transceiver RJ45 connector labeled "M&C LAN". Turn the transceiver power supply on and wait approximately 5-10 seconds. In the **ComBlock Control Center** window, click on the left-most button and select LAN as primary communication media. The default IP address is 172.16.1.128.

In the **ComBlock Control Center** window detect the ComBlock module(s) by clicking the  $\checkmark$  *Detect* button, next click to highlight the COM-1905 module to be configured, next click the M *Settings* button to display the *Settings* window shown below.

| ComBlock Contro     | ol Center                                                                       |   |

|---------------------|---------------------------------------------------------------------------------|---|

| File Operations Fun | ctions Help                                                                     |   |

| * 🛰 🖻 🀝 (           | 1 🐜 🗐 🚇                                                                         |   |

| COM1905A F          |                                                                                 | × |

|                     | RF frequencies Modulation & FEC encoding Demodulation & FEC decoding IP network |   |

|                     | Frequency index: 0 [0-7] RF frequency: 925000000 Hz                             |   |

|                     | Tx ALC target level: 4095 0-4095 ITransmitter on                                |   |

|                     |                                                                                 |   |

|                     | Frequency index: 1 [0-7] RF frequency: 120000000 Hz                             |   |

|                     | Initial LNA gain: 1023 0-1023 Initial RF gain: 0 0-4095                         |   |

|                     | Initial IF gain: 0 0-4095 RF AGC: AGC on 🗸                                      |   |

|                     | IF AGC: AGC on 🗸 LNB supply: Off 🗸                                              |   |

|                     | General                                                                         |   |

|                     | Frequency 0 925000000 Frequency 1 1200000000                                    |   |

|                     | Frequency 2 140000000 Frequency 3 160000000                                     |   |

|                     | Frequency 4 150000000 Frequency 5 180000000                                     |   |

|                     | Frequency 6 200000000 Frequency 7 0                                             |   |

| COM-1905 simulation | Restore Default Apply Ok Advan Cancel                                           |   |

| COM1905 PSK modem Basic Settings                                     | ×                                     |

|----------------------------------------------------------------------|---------------------------------------|

| RF frequencies Modulation & FEC encoding Demodulation & FEC decoding | IP network                            |

| Symbol rate: 20000000 Symbols/s T                                    | x center frequency offset: 0 Hz       |

| Modulation: QPSK v                                                   |                                       |

| Signal amplitude: 30000 range 0-65536 No                             | oise amplitude: 0 range 0-65536       |

| Input Selection: IP router WAN interface 🗸 🗸                         | Tx spectrum inversion                 |

|                                                                      |                                       |

| FEC encoding enabled                                                 |                                       |

| Restore Default Apply Ok                                             | Advan Cancel                          |

|                                                                      |                                       |

| COM1905 PSK modem Basic Settings                                     | ×                                     |

| RF frequencies Modulation & FEC encoding Demodulation & FEC decoding | I IP network                          |

| Input center frequency: 0 Hz                                         | AGC response time: 12 0 - 14          |

| Symbol rate: 20000000 Symbols/s                                      | Spectrum inversion                    |

| Symbol decoding: QPSK 🧹 Fre                                          | equency acquisition range: 2500000 Hz |

| FEC decoding enabled                                                 |                                       |

Restore Default

Apply

Ok

Advan...

Cancel

| COM1905 PSK modem Basic Settings                           |                                                 |  |

|------------------------------------------------------------|-------------------------------------------------|--|

| RF frequencies Modulation & FEC encoding Demodulation & FE | EC decoding IP network                          |  |

| LAN LAN1 IP address: 172, 16, 1, 128                       | LAN2 IP address: 172 16 1 129                   |  |

| Subnet1 mask: 255 255 255 0                                | Subnet2 mask: 255 255 255 0                     |  |

|                                                            | Default gateway2: 172 16 1 3                    |  |

|                                                            | IP multicast IP directed broadcast IP broadcast |  |

| QoS Bandwidth Management                                   |                                                 |  |

| EF PHB bandwidth quota: 18 %                               | bits/s                                          |  |

| AF1 PHB bandwidth quota: 20.3 %                            | bits/s                                          |  |

| AF2 PHB bandwidth quota: 20.3 %                            | bits/s                                          |  |

| AF3 PHB bandwidth quota: 20.3 %                            | bits/s                                          |  |

| AF4 PHB bandwidth quota: 20.3 %                            | bits/s                                          |  |

| DHCP SERVER                                                |                                                 |  |

| ☑ DHCP server enable                                       | IP pool start address: 172 16 1 170             |  |

| IP pool size: 6 Lease time (s) 3600                        |                                                 |  |

| Router address: 172 16 1 129 DNS address: 8 8 8 8          |                                                 |  |

| Restore Default Apply                                      | Ok Advan Cancel                                 |  |

# Configuration (Advanced)

Alternatively, users can access the full set of configuration features by specifying 8-bit control registers as listed below. These control registers can be set manually through the ComBlock Control Center "Advanced" configuration or by software using the ComBlock API (see <a href="http://www.comblock.com/download/M&C\_reference.pdf">www.comblock.com/download/M&C\_reference.pdf</a>)

All control registers are read/write. Definitions for the <u>Control registers</u> and <u>Status registers</u> are provided below.

#### **Control Registers**

The module configuration parameters are stored in volatile (SRT command) or non-volatile memory (SRG command). The stored configuration is automatically loaded up at power up. All control registers are read/write.

# Note: several multi-byte fields like the IP addresses are enacted upon (re-)writing to the last control register (REG148)

Several key parameters are computed on the basis of the 160 MHz ADC clock  $\mathbf{f}_{clk\_adc}$  or the 120 MHz internal processing clock  $\mathbf{f}_{clk\_p}$ .

| RF                     | Configuration                                                                                |

|------------------------|----------------------------------------------------------------------------------------------|

| Stored frequency       | Preselected transmitter or receiver frequency $f_0$ . (one of eight stored frequencies)      |

| f <sub>0</sub>         | Valid range 925 MHz – 2.175 GHz, expressed in Hz.                                            |

|                        |                                                                                              |

|                        | REG0: bit 7:0 (LSB)                                                                          |

|                        | REG1: bit 15:8                                                                               |

|                        | REG2: bit 23:16                                                                              |

|                        | REG3: bit 31:24 (MSB)                                                                        |

| Receiver frequency     | Use to switch the receiver center frequency among preselected values.                        |

| selection              | Range 0 through 7                                                                            |

|                        | REG6(2:0)                                                                                    |

| Transmitter frequency  | Use to switch the transmitter center frequency among preselected values.                     |

| selection              | Range 0 through 7                                                                            |

|                        | The rx/tx frequencies change is enacted upon writing to REG6.                                |

|                        | REG6(6:4)                                                                                    |

| Stored frequency       | Seven additional preselected frequencies                                                     |

| f <sub>x</sub>         | x = 1 through 7                                                                              |

|                        | Same format as $f_0$ .                                                                       |

|                        | REG $(3+4*x)$ : bits 7:0 (LSB)                                                               |

|                        | REG(4+4*x): bits 15:8                                                                        |

|                        | REG(5+4*x): bits 23:16                                                                       |

|                        | REG(6+4*x): bits 31:24 (MSB)                                                                 |

| Receiver RF Gain       | Initial RF gain (before the RF AGC takes over). 12-bit.                                      |

|                        | 0 for the minimum gain, 4095 for the maximum gain.                                           |

|                        | The receiver RF gain change is enacted upon writing to REG5.                                 |

|                        | REG4: bits 7:0 (LSB)                                                                         |

|                        | REG5(3:0): bits 11:8                                                                         |

| Receiver IF Gain       | Initial IF gain (before the IF AGC takes over). 12-bit.                                      |

|                        | 0 for the minimum gain, 4095 for the maximum gain.                                           |

|                        | The receiver IF gain change is enacted upon writing to REG36.                                |

|                        | REG35: bits 7:0 (LSB)                                                                        |

|                        | REG36(3:0): bits 11:8                                                                        |

| Receiver LNA Gain      | LNA gain 10-bit.                                                                             |

|                        | 0 for the minimum gain, 1023 for the maximum gain.                                           |

|                        | The receiver IF gain change is enacted upon writing to REG41.                                |

|                        | REG40: bits 7:0 (LSB)                                                                        |

|                        | REG41(3:0): bits 11:8                                                                        |

| Transmitter ALC target | The transmit gain is automatically adjusted so that the measured tx power equals this field. |

|                        | The transmitter gain change is enacted upon writing to REG38.                                |

|                        | REG37: bits 7:0 (LSB)                                                                        |

|                        | REG38(3:0): bits 11:8                                                                        |

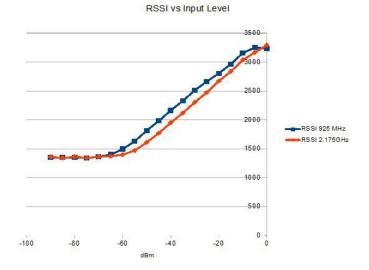

| Receiver LNA AGC loop  | 0 = open loop. LNA path gain is fixed by control registers.                                  |

|                        | 1 = AGC on. Gain is adjusted on the basis of the RSSI measurement.                           |

|                        | REG39(0)                                                                                     |

| Receiver RF AGC loop   | 0 = open loop. RF path gain is fixed by control registers.                                   |

|                        | 1 = AGC on. Out-of-range conditions are detected at the RF mixer and IF power detector.      |

|                                          | REG39(1)                                                                                                                                                                         |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receiver IFAGC loop                      | 0 = open loop. IF1 path gain is fixed by control registers.                                                                                                                      |

| × ×                                      | 1 = AGC on. Out-of-range conditions are detected at the IF power detector.                                                                                                       |

|                                          | REG39(3:2)                                                                                                                                                                       |

| Transmitter ON                           | 0 = off                                                                                                                                                                          |

|                                          |                                                                                                                                                                                  |

| LND (12/101/) ON                         | REG39(6)                                                                                                                                                                         |

| LNB power (13/18V) ON                    | The transceiver is capable of supplying up to 500mA at 13VDC or 18VDC to an external LNB.<br>This supply voltage is multiplexed with the RF input signal onto the "RF Rx" input. |

|                                          | 0 = LNB supply off                                                                                                                                                               |

|                                          | 1 = LNB supply on                                                                                                                                                                |

|                                          | Warning: Enabling the LNB supply may cause damage to test equipment unless a                                                                                                     |

|                                          | DC block is used.                                                                                                                                                                |

|                                          | REG43(0)                                                                                                                                                                         |

| LNB power selection                      | 0 = 13V                                                                                                                                                                          |

|                                          | 1 = 18V                                                                                                                                                                          |

|                                          | REG43(1)                                                                                                                                                                         |

| General Parameters                       | Configuration                                                                                                                                                                    |

| Internal/External<br>frequency reference | 10 MHz output generated from 10 MHz input (-B firmware option) or 19.2 MHz TCXO (-A firmware option)                                                                             |

|                                          | REG46(1): enable(1)/disable(0) CLKREF_OUT (special connector on front-panel)                                                                                                     |

|                                          | REG46(2): enable(1)/disable(0) CLK LNB (multiplexed with received signal)                                                                                                        |

|                                          | REG46(3): enable(1)/disable(0) CLK TX (multiplexed modulated transmit signal + 10 MHz)                                                                                           |

| FEC                                      |                                                                                                                                                                                  |

| FEC encoding                             | 0 = bypassed                                                                                                                                                                     |

| The encounty                             | 1 = FEC encoding enabled                                                                                                                                                         |

|                                          |                                                                                                                                                                                  |

|                                          | REG47(0)                                                                                                                                                                         |

| FEC decoding                             | 0 = bypassed                                                                                                                                                                     |

|                                          | 1 = FEC decoding enabled                                                                                                                                                         |

|                                          | REG47(1)                                                                                                                                                                         |

| Convolutional encoding                   | When the FPGA is configured with the convolutional/Viterbi FEC firmware version                                                                                                  |

| constraint length K and                  | 0000 = (K=5, R=1/7)                                                                                                                                                              |

| rate R                                   |                                                                                                                                                                                  |

|                                          |                                                                                                                                                                                  |

|                                          | Intelsat IESS-308/309                                                                                                                                                            |

|                                          |                                                                                                                                                                                  |

|                                          | 0001 = (K = 7, R = 1/2, Intelsat)                                                                                                                                                |

|                                          | 0010 = (K = 7, R = 2/3, Intelsat)                                                                                                                                                |

|                                          | 0011 = (K = 7, R = 3/4, Intelsat)                                                                                                                                                |

|                                          |                                                                                                                                                                                  |

|                                          | 0100 = (K = 7, R = 5/6, Intelsat)                                                                                                                                                |

|                                          | 0101 = (K = 7, R = 7/8, Intelsat)                                                                                                                                                |

|                                          |                                                                                                                                                                                  |

|                                          |                                                                                                                                                                                  |

|                                          | 0110 = (K = 9, R = 1/3)                                                                                                                                                          |

|                                          | 0111 = (K = 9, R = 1/2)                                                                                                                                                          |

|                                          |                                                                                                                                                                                  |

|                                          | 1000 = (K = 9, R = 2/3)                                                                                                                                                          |

|                                          |                                                                                                                                                                                  |

|                                          | DVB ETS 300 421                                                                                                                                                                  |

|                                          | DVB ETS 300 744                                                                                                                                                                  |

|                                          |                                                                                                                                                                                  |

|                                               | 1010 = (K = 7, R=1/2, DVB)<br>1011 = (K = 7, R=1/2, CCSDS)                                                                                                  |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                               | 1100 = (K = 7, R=2/3, CCSDS/DVB)                                                                                                                            |

|                                               | 1101 = (K = 7, R=3/4, CCSDS/DVB)                                                                                                                            |

|                                               | 1110 = (K = 7, R=5/6, CCSDS/DVB)                                                                                                                            |

|                                               | 1111 = (K = 7, R=7/8, CCSDS/DVB)                                                                                                                            |

|                                               | REG54(4:1)                                                                                                                                                  |

| Convolutional encoder:                        | When the FPGA is configured with the convolutional/Viterbi FEC firmware version                                                                             |

| Differential Encoding                         | Differential encoding is useful in removing phase ambiguities at the PSK demodulator, at the expense of doubling the bit error rate.                        |

|                                               | When enabled, the differential decoding must be enabled at the receiving end.                                                                               |

|                                               | There is no need to use the differential encoding to remove phase ambiguities at the PSK demodulator when the Viterbi decoder and HDLC decoder are enabled. |

|                                               | 0 = disabled                                                                                                                                                |

|                                               | 1 = enabled                                                                                                                                                 |

|                                               | REG54 (5)                                                                                                                                                   |

| Viterbi decoding                              | When the FPGA is configured with the convolutional/Viterbi FEC firmware version                                                                             |

| constraint length K and rate R                | 0001 = (K = 7, R = 1/2, Intelsat)                                                                                                                           |

|                                               | 0010 = (K = 7, R = 2/3, Intelsat)                                                                                                                           |

|                                               | 0011 = (K = 7, R = 3/4, Intelsat)                                                                                                                           |

|                                               | 0100 = (K = 7, R = 5/6, Intelsat)                                                                                                                           |

|                                               | 0101 = (K = 7, R = 7/8, Intelsat)                                                                                                                           |

|                                               | 1010 = (K = 7, R = 1/2, DVB)                                                                                                                                |

|                                               | 1011 = (K = 7, R=1/2, CCSDS)                                                                                                                                |

|                                               | 1100 = (K = 7, R=2/3, CCSDS/DVB)                                                                                                                            |

|                                               | 1101 = (K = 7, R=3/4, CCSDS/DVB)                                                                                                                            |

|                                               | 1110 = (K = 7, R = 5/6, CCSDS/DVB)                                                                                                                          |

|                                               | 1111 = (K = 7, R = 7/8, CCSDS/DVB)                                                                                                                          |

|                                               | REG55(4:1)                                                                                                                                                  |

| Viterbi decoding:<br>Differential Decoding    | When the FPGA is configured with the convolutional/Viterbi FEC firmware version                                                                             |

|                                               | 0 = disabled                                                                                                                                                |

|                                               | l = enabled                                                                                                                                                 |

| The second second second                      | REG55(5)                                                                                                                                                    |

| Turbo code encoder<br>Uncoded payload size in | When the FPGA is configured with the turbo codec firmware version                                                                                           |

| Bytes.                                        | Preferred sizes: 14, 63, 250 Bytes<br>Must NOT be an integer multiple of 15                                                                                 |

|                                               | Maximum 254 Bytes.                                                                                                                                          |

|                                               | REG95                                                                                                                                                       |

| Turbo code encoder rate                       | $0 = \operatorname{rate} \frac{1}{3}$                                                                                                                       |

|                                               | 1 = rate  1/2 $2 = rate  2/3$                                                                                                                               |

| [                                                |                                                                                                    |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------|

|                                                  | 3 = rate  3/4                                                                                      |

|                                                  | 4 = rate  4/5                                                                                      |

|                                                  | 5 = rate  5/6                                                                                      |

|                                                  | 6 = rate 6/7                                                                                       |

|                                                  | 7 = rate 7/8                                                                                       |

|                                                  | REG96(3:0)                                                                                         |

| Turbo code encoder<br>Encoded frame size in bits | Encoded frame size in bits. For example: when payload size is 14, rate 1/3, the encoded frame size |

| Encoded frame size in bits                       | is $14*8*3 = 336$ bits. Does not include any periodic synchronization field.                       |

|                                                  |                                                                                                    |

|                                                  | REG97 LSB                                                                                          |

| Turbo code decoder                               | REG98(6:0) (MSB)                                                                                   |

| Decoded payload size in                          | Preferred sizes: 14, 63, 250 Bytes                                                                 |

| Bytes.                                           | Must NOT be an integer multiple of 15                                                              |

| 2 ) ((0).                                        | Maximum 254 Bytes.                                                                                 |

|                                                  | REG99                                                                                              |

| Turbo code decoder rate                          | 0 = rate  1/3                                                                                      |

|                                                  | 1 = rate 1/2                                                                                       |

|                                                  | $2 = rate \frac{1}{2}$                                                                             |

|                                                  | 3 = rate 3/4                                                                                       |

|                                                  | 4 = rate  4/5                                                                                      |

|                                                  | 5 = rate  5/6                                                                                      |

|                                                  | 6 = rate  6/7                                                                                      |

|                                                  | 7 = rate  7/8                                                                                      |

|                                                  | REG100(3:0)                                                                                        |

| Turbo code decoder                               | Coded frame size in bits. For example: when payload size is 14, rate 1/3, the coded frame size is  |

| Coded frame size in bits                         | 14*8*3 = 336 bits. Does not include any periodic synchronization field.                            |

|                                                  |                                                                                                    |

|                                                  | REG101 LSB                                                                                         |

|                                                  | REG102(6:0) (MSB)                                                                                  |

| Turbo code decoder                               | 1 – 15. Typical settings is 7.                                                                     |

| maximum number of                                | Must be an odd number                                                                              |

| iterations                                       | REG103                                                                                             |

| Scrambling                                       |                                                                                                    |

| Scrambler enabled                                | Scrambling is performed after FEC encoding. Sync marker insertion is required in order for the     |

|                                                  | descrambler to synchronize.                                                                        |

|                                                  | 0 = bypassed                                                                                       |

|                                                  |                                                                                                    |

|                                                  | 1 = enabled                                                                                        |

|                                                  | REG47(2)                                                                                           |

| Descrambler enabled                              | Descrambling is performed prior to FEC decoding. Sync marker insertion is required in order for    |

|                                                  | the descrambler to synchronize.                                                                    |

|                                                  | 0 = bypassed                                                                                       |

|                                                  | 1 = enabled                                                                                        |

|                                                  | REG47(3)                                                                                           |

|                                                  |                                                                                                    |

| Scrambler key                                    | 32-bit key                                                                                         |

|                                                  | REG59-REG62                                                                                        |

| Descrambler key                                  | 32-bit key                                                                                         |

|                                                  | REG63-REG66                                                                                        |

| PSK Demodulator                                  | Configuration                                                                                      |

| Parameters                                       | gii iliuu                                                                                          |

| Tx-Rx loopback                                   | REG42(0): enable (1) or disable(0) loopback test mode                                              |

| Input frequency offset                           | Modulated signal center frequency offset. Typically 0.                                             |

| $(\mathbf{f_{c_rx}})$                            | 32-bit signed integer (2's complement representation) expressed as                                 |

| ( <b>*c_rx</b> )                                 | $f_{c,rx} * 2^{32} / f_{elk,ade}$                                                                  |

|                                                  | Le_rx $\sim$ / Leik_ade                                                                            |

|                                                  | I                                                                                                  |

|                                         | DEC05. LOD                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | REG85: LSB<br>REG86                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                         | REG86<br>REG87                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                         | REG88: MSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Frequency acquisition<br>range (scan)   | The demodulator natural frequency acquisition range is around 20% of the symbol range (depending on modulation, SNR). The frequency acquisition range can be extended by frequency scanning. Scanning steps are spaced ( $f_{symbol rate rx}$ /4) apart. The user can thus trade-off acquisition time versus frequency acquisition range by specifying the number of scanning steps here.<br>For example, 4 steps yield a frequency acquisition range of +/- $f_{symbol rate rx}$ |

|                                         | REG94                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AGC response                            | REG89(4:0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Spectrum inversion                      | Invert Q bit.<br>0 = off<br>1 = on<br>REG89(5)                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BPSK / QPSK decoding                    | 0 = BPSK<br>1 = QPSK<br>2 = OQPSK<br>REG89(7:6)                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Symbol rate                             | f <sub>symbol_rate</sub> * 2 <sup>32</sup> / f <sub>clk_adc</sub>                                                                                                                                                                                                                                                                                                                                                                                                                 |

| f <sub>symbol_</sub> rate               | REG90 = bits 7 – 0 (LSB)<br>REG91 = bits 15 – 8<br>REG92 = bits 23 – 16<br>REG93 = bits 31 – 24 (MSB)                                                                                                                                                                                                                                                                                                                                                                             |

| Detect and remove                       | Enabled (1)/ Disabled(0)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| periodic sync marker                    | A periodic sync marker is required for synchronizing the turbo code decoder and the descrambler.<br>It also helps resolving the demod phase ambiguity. Generally enabled unless compatibility with<br>other systems is needed.<br>REG47(5)                                                                                                                                                                                                                                        |

| PSK Modulator<br>Parameters             | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Parameters Processing clock             | Modulator processing clock. Also serves as DAC sampling clock.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>f</b> <sub>elk_tx</sub>              | Expressed as as $\mathbf{f}_{\mathbf{clk}_{\mathbf{t}}\mathbf{x}} = 120 \text{ MHz} * \text{M} / (\text{D} * \text{O}))$ where                                                                                                                                                                                                                                                                                                                                                    |

|                                         | D is an integer divider in the range 1 - 106                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                         | M is a multiplier in the range 2.0 to 64.0 by steps of 1.0. Fixed point format 7.3                                                                                                                                                                                                                                                                                                                                                                                                |

|                                         | O is a divider in the range 2.0 to 128.0 by steps of 1.0. Fixed point format 7.3                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                         | Note: the graphical use interface computes the best values for M, D and O.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                         | $\mathbf{f}_{\text{clk}_tx}$ recommended range 80-160 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                         | REG48(6:0) = D                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                         | REG49 = M(7:0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                         | REG50(1:0) = M(9:8)                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                         | REG51 = O(7:0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| C. autoritaria                          | REG52(1:0) = O(10:8)                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Symbol rate<br>f <sub>symbol_rate</sub> | The modulator symbol rate is in the form $\mathbf{f}_{symbol rate tx} = \mathbf{f}_{clk\_tx} / 2^n$<br>where n ranges from 1 (2 samples per symbol) to 15 (symbol rate = $\mathbf{f}_{clk\_tx} / 32768$ ).<br>n is defined in REG53(3:0)                                                                                                                                                                                                                                          |

| Digital Signal gain                     | 16-bit amplitude scaling factor for the modulated signal.<br>The maximum level should be adjusted to prevent saturation. The settings may vary slightly with the selected symbol rate. Therefore, we recommend <u>checking for saturation at the D/A converter</u> when changing either the symbol rate or the signal gain. (see status registers SREG39)                                                                                                                         |

|                                 | Enacted upon writing the MSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | REG67 = LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                 | REG68 = MSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Additive White Gaussian         | 16-bit amplitude scaling factor for additive white Gaussian noise.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Noise gain                      | Because of the potential for saturation, please <u>check for saturation at the D/A converter</u> when                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                 | changing this parameter. (see status registers SREG39)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                 | REG69 = LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Modulation type                 | REG70 = MSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Modulation type                 | Modulation type $0 = BPSK$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                 | 1 = QPSK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                 | 2 = OQPSK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Spectrum inversion              | REG71(5:0)<br>Invert Q bit. (Inverts the modulated spectrum only, not the subsequent frequency translation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Spectrum inversion              | 0 = off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                 | 1 = on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                 | REG71(6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Input selection / format,       | Select the origin of the modulator input data stream.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| test modes                      | 0 = IP router WAN interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                 | 1 = test sequence: internal generation of 2047-bit periodic pseudo-random bit sequence as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                 | <ul><li>modulator input. (overrides external input bit stream)</li><li>2 = test sequence: unmodulated carrier. This helps checking the follow-on RF modulator.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                 | 3 = input data from remote TCP client via the built-in LAN1/TCP server at port 1024                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                 | 5 – input data from remote TCF cheft via the buft-in LAN1/TCF server at port 1024                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                 | Test sequences override external input bit stream.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                 | REG72(2:0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Output Center                   | Fine tuning of center frequency. Typically 0 Hz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| frequency $(\mathbf{f}_{c_tx})$ | 32-bit signed integer (2's complement representation) expressed as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                 | $\mathbf{f}_{c_tx} * 2^{32} / \mathbf{f}_{clk_tx}$<br>For a clean output waveform, we recommend keeping the maximum frequency (center frequency +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |