# COM-1827 CPM MODEM

# **Key Features**

- Modulator/demodulator for continuous-phase modulation (CPM), including

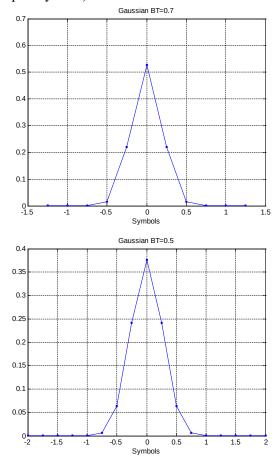

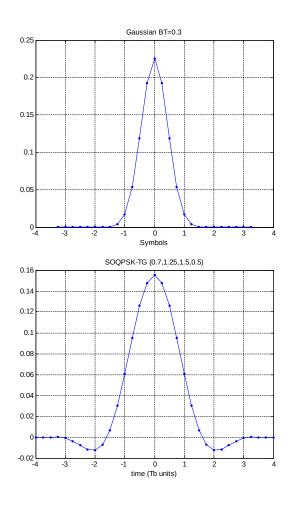

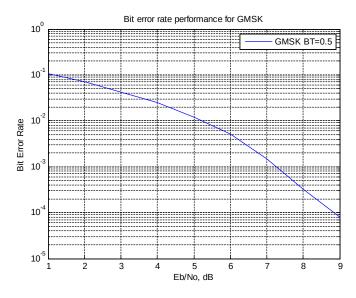

- MSK, GMSK (BT = 0.7,0.5,0.3 and 0 0.25),

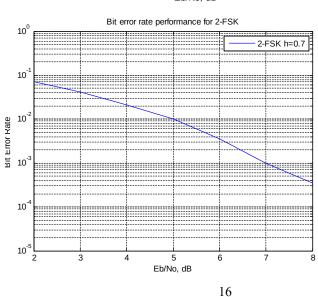

- 0 FSK, GFSK,

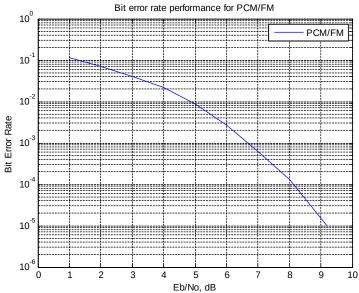

- PCM/FM 0

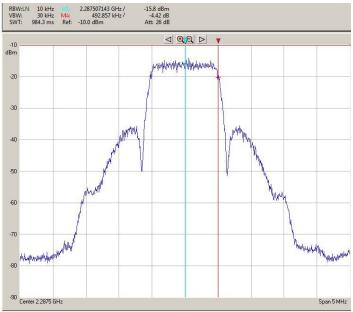

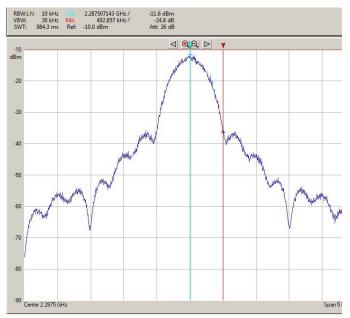

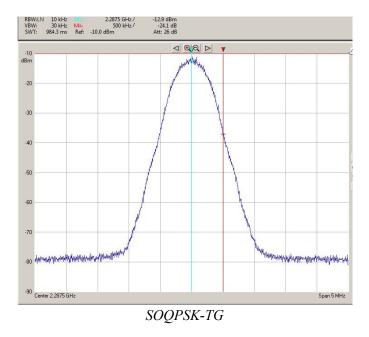

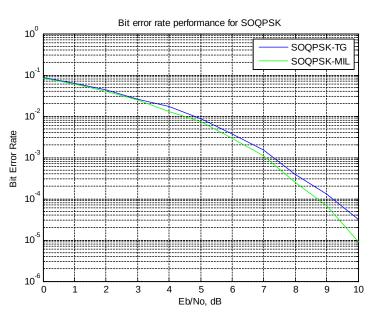

- SOQPSK-MIL, SOQPSK-TG 0

- These constant envelope modulations are ideal for operation through power amplifiers near saturation.

- Flexible programmable features:

- Symbol rate up to 39.5 Msymbols/s 0

- Modulation index h [0.125 to 4] 0

- 0 Frequency pulse type (rectangular, Gaussian, raised cosine, etc)

- Coherent demodulation for h = 0.5Non-coherent demodulation for all other modulation indices h.

- Frequency acquisition range > +/- 12% of symbol rate. Tracking symbol rates over +/-50ppm around nominal setting.

- Implementation loss < 0.5 dB down to Eb/No = 2dB. 4-bit soft-decision output (SOVA) for use by follow-on error correction.

- Convolutional or Turbo-code FEC error correction

- TCP server for modulator data input and demodulator output. UDP server for demodulator output.

- Built-in tools: PRBS-11 pseudo-random test sequence, BER tester, AWGN generator, internal loopback mode, carrier frequency error measurement.

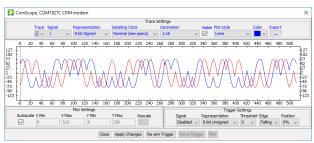

- **ComScope** –enabled: key internal signals can be captured in real-time and displayed on host computer.

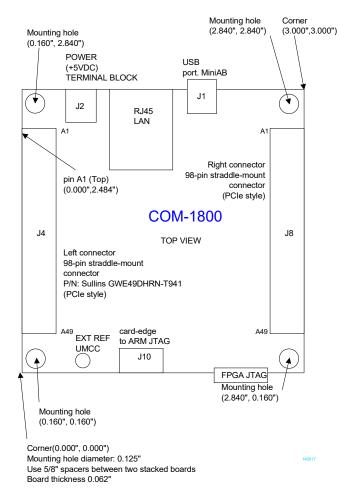

Connectorized 3"x 3.5" module for ease of • prototyping. Single 5V supply with reverse voltage and overvoltage protection. Interfaces with 3.3V LVTTL logic.

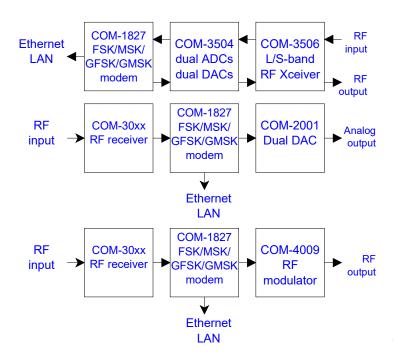

# Typical assemblies

MSS • 845 Quince Orchard Boulevard Ste N • Gaithersburg, Maryland 20878-1676 • U.S.A. Telephone: (240) 631-1111 www.ComBlock.com © MSS 2023 Issued 6/18/2023

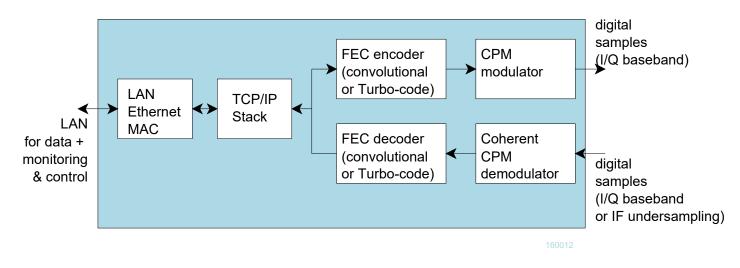

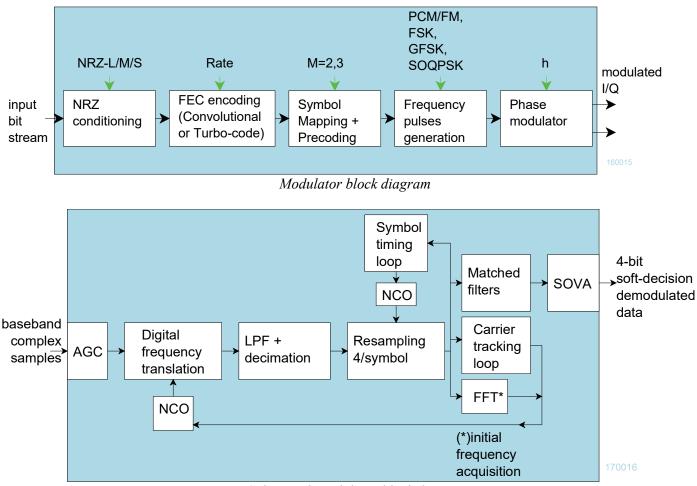

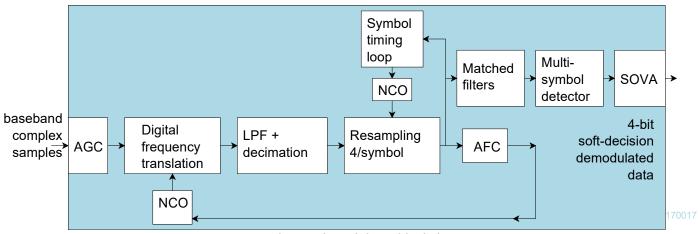

## **Block Diagrams**

Overall block diagram

Coherent demodulator block diagram

Non-coherent demodulator block diagram

# Configuration

An entire ComBlock assembly comprising several ComBlock modules can be monitored and controlled centrally over a single connection with a host computer. Connection types include built-in types:

• USB, TCP-IP/LAN

or connections via adjacent ComBlocks

The module configuration is stored in non-volatile memory.

# **Configuration (Basic)**

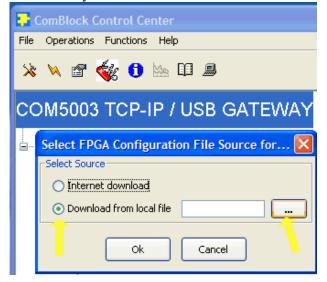

The easiest way to configure the COM-1827 is to use the **ComBlock Control Center** software supplied with the module on CD. In the **ComBlock Control Center** window detect the ComBlock module(s) by clicking the *Detect* button, next click to highlight the COM-1827 module to be configured, next click the Settings button to display the Settings window shown below. ComBlock Control Center

File Operations Functions Help

🔆 🔌 🖀 🎪 🗊 🖄 🕮

## COM1827C CPM modem

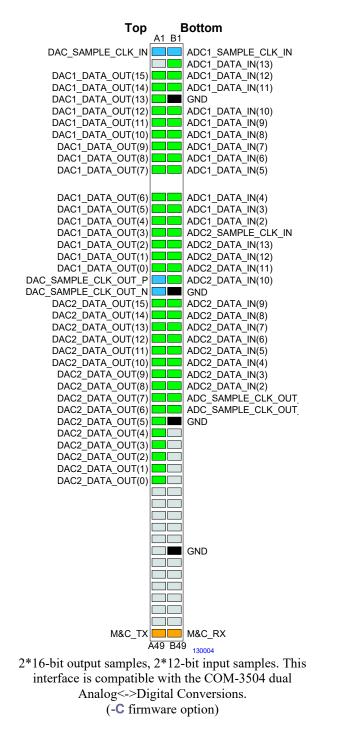

# COM3504 Dual Analog <-> Digital Conversions

# COM3506 [400MHz - 3GHz] Transceiver

| COM1827 CPM modem Basic Settings                                       |                                              |

|------------------------------------------------------------------------|----------------------------------------------|

| Modulation & FEC encoding Demodulation & FEC decoding IP network       |                                              |

| Input Selection: Test mode:internal PRBS-11 test sequence $\checkmark$ | Data Format: NRZ-L 🗸 🗸                       |

| Symbol rate: 1000000 Symbols/s                                         | Modulation index: 0.5 range 0 - 8.0          |

| Premodulation frequency shaping filter: Gaussian (GFSK/GMSK) BT=0.3 ~  |                                              |

| Tx center frequency offset: 0 Hz                                       | Tx spectrum inversion Modulator ON           |

| Signal amplitude: 20000 range 0-65536                                  | Noise amplitude: 0 range 0-65536             |

| FEC encoding enabled                                                   | Turbo code encoder: $ m [rate 3/4 \ {\sim}]$ |

| External 10MHz frequency reference                                     |                                              |

| Restore Default Apply                                                  | Ok Advan Cancel                              |

| COM1827 CPM modem Basic Settings X                                                                                          |                                                    |  |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|

| Modulation & FEC encoding Demodulation & FEC decoding IP network                                                            |                                                    |  |

| Sampling dock to external ADC/Receiver: 🔽 160000000 Samples/s                                                               | Measured input sampling rate: 1599999999 Samples/s |  |

| Input Selection: IF input (undersampling) $\checkmark$                                                                      | AGC response time: 12 0 - 14                       |  |

| Input center frequency: 140000000 Hz                                                                                        | AFC Spectrum inversion                             |  |

| Symbol rate: 1000000 Symbols/s                                                                                              | Modulation index: 0.5 range 0 - 8.0                |  |

| Premodulation frequency shaping filter: PCM/FM (premod LPF, 3dB cutoff at BT/2 $\checkmark$ Data Format: NRZ-L $\checkmark$ |                                                    |  |

| FEC decoding enabled                                                                                                        | Turbo code decoder: Fate 1/3 ~                     |  |

| Restore Default Apply                                                                                                       | Ok Advan Cancel                                    |  |

| COM1827 CPM modem Basic Settings             |                                   | × |

|----------------------------------------------|-----------------------------------|---|

| Modulation & FEC encoding Demodulation & FEC | decoding IP network               |   |

| LAN                                          | LAN IP address: 172 16 1 128      |   |

|                                              | Subnet1 mask: 255 255 255 0       |   |

|                                              | Default gateway: 172 16 3         |   |

|                                              | MAC address: 02:42:3A:F0:54:00    |   |

| Resto                                        | ore Default Apply Ok Advan Cancel |   |

# **Configuration (Advanced)**

Alternatively, users can access the full set of configuration features by specifying 8-bit control registers as listed below. These control registers can be set manually through the ComBlock Control Center or by software using the ComBlock API (see <a href="http://www.comblock.com/download/M&C\_reference.pdf">www.comblock.com/download/M&C\_reference.pdf</a>)

All control registers are read/write. Definitions for the <u>Control registers</u> and <u>Status registers</u> are provided below.

# **Control Registers**

The module configuration parameters are stored in volatile (SRT command) or non-volatile memory (SRG command). All control registers are read/write.

Several key parameters are computed on the basis of the receive sampling clock  $\mathbf{f}_{clk_rx}$  and transmit sampling clock  $\mathbf{f}_{clk_tx}$  or the 125 MHz internal processing clock f<sub>clk\_p</sub>.

| General                                     |                                                                                                                                                                                 |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameters                                  | Configuration                                                                                                                                                                   |

| Internal/External<br>frequency<br>reference | 0 = internal TCXO as frequency<br>reference.<br>1 = external. Use the 10 MHz<br>clock externally supplied through<br>the J7 SMA connector as<br>frequency reference.<br>REG0(7) |

| Modulator                    |                                                                                                                                             |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Parameters                   | Configuration                                                                                                                               |

| Input selection<br>INPUTS SE | 1 = LAN TCP port 1024                                                                                                                       |

| L                            | 3 = internal pseudo-random test sequence                                                                                                    |

|                              | 4 = zero input                                                                                                                              |

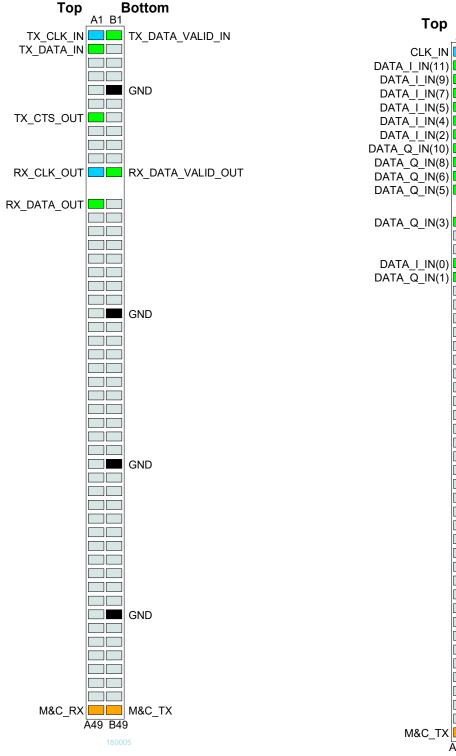

|                              | 5 = serial data bit input + bit clock<br>output, left connector                                                                             |

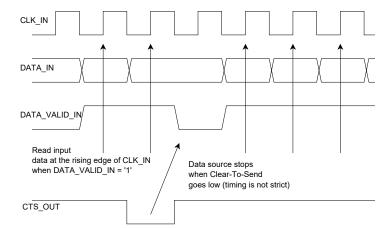

|                              | 6 = clock synchronous serial input<br>(serial data bit, enable, Clear-To-<br>Send input flow control, synchronous<br>clock), left connector |

|                              | 7 = unmodulated test mode (carrier only)                                                                                                    |

|                              | REG0(3:0)                                                                                                                                   |

| Data formatting              | 0 = NRZ-L                                                                                                                                   |

|                              | 1 = NRZ-M                                                                                                                                   |

|                              | 2 = NRZ-S                                                                                                                                   |

|                              | REG0(6:4)                                                                                                                                   |

| Transmit<br>sampling clock,<br>frequency<br>$f_{clk_tx}$ Modulator processing clock. Also<br>serves as DAC sampling clock.<br>Expressed as as $f_{clk_tx} = 160$ MHz *<br>$M / (D * 0)$ ) where<br>D is an integer divider in the range 1 -<br>106<br>M is a multiplier in the range 2.0 to<br>64.0 by steps of 1.0. Fixed point<br>format 7.3<br>O is a divider in the range 2.0 to<br>128.0 by steps of 1.0. Fixed point<br>format 7.3<br>Note: the graphical use interface<br>computes the best values for M, D<br>and O. $f_{clk_tx}$ recommended range 80-160<br>MHz.REG1(6:0) = D<br>REG2 = M(7:0)<br>REG3(1:0) = M(9:8)<br>REG4 = O(7:0)<br>REG5(2:0) = O(10:8)Symbol rate<br>fymbol_ratefymbol_ratefymbol_ratefymbol_ratefymbol_rateformation<br>frequency<br>shaping filterPremodulation<br>frequency<br>shaping filterO<br>standardFrequency<br>shaping filterReG74 (LSB) - REG77 (MSB)<br>O = rectangle (FSK, GMSK),<br>BT=0.7<br>B = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| frequency<br>fek_txExpressed as as $f_{dk_tx} = 160$ MHz *<br>M / (D * 0)) where<br>D is an integer divider in the range 1 -<br>106<br>M is a multiplier in the range 2.0 to<br>64.0 by steps of 1.0. Fixed point<br>format 7.3<br>O is a divider in the range 2.0 to<br>128.0 by steps of 1.0. Fixed point<br>format 7.3<br>Note: the graphical use interface<br>computes the best values for M, D<br>and O.felk_txrecommended range 80-160<br>MHz.REG1(6:0) = D<br>REG2 = M(7:0)<br>REG3(1:0) = M(9:8)<br>REG4 = O(7:0)<br>REG5(2:0) = O(10:8)Symbol_rate<br>fymbol_rateNominal symbol rate, defined as<br>f_symbol_rate * 2 <sup>32</sup> / f_ck_txThroughout this document, the<br>symbol period is defined as the time<br>to send one element out of the M-<br>symbol alphabet. In the case of<br>SOQPSK, a symbol represents only<br>one information bit.Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.3 |

| $f_{ek_{L}x}$ Expressed as as $f_{ek_{L}x} = 100$ MH2 *<br>M / (D * O)) where<br>D is an integer divider in the range 1 -<br>106<br>M is a multiplier in the range 2.0 to<br>64.0 by steps of 1.0. Fixed point<br>format 7.3<br>O is a divider in the range 2.0 to<br>128.0 by steps of 1.0. Fixed point<br>format 7.3<br>Note: the graphical use interface<br>computes the best values for M, D<br>and O. $f_{elk_{L}x}$ recommended range 80-160<br>MHz.REG1(6:0) = D<br>REG2 = M(7:0)<br>REG3(1:0) = M(9:8)<br>REG4 = O(7:0)<br>REG5(2:0) = O(10:8)Symbol rate<br>fymbol_ratefymbol_ratefymbol_ratefymbol rate<br>formation bit.REG74 (LSB) - REG77 (MSB)<br>O = rectangle (FSK, MSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                    |

| $M / (D = 0)) \text{ Where}$ $D \text{ is an integer divider in the range 1 - 106}$ $M \text{ is a multiplier in the range 2.0 to} 64.0 \text{ by steps of 1.0}. Fixed point} format 7.3$ $O \text{ is a divider in the range 2.0 to} 128.0 \text{ by steps of 1.0}. Fixed point} format 7.3$ $Note: the graphical use interface computes the best values for M, D and O.$ $f_{elk, ts} \text{ recommended range 80-160}$ $MHz.$ $REG1(6:0) = D$ $REG2 = M(7:0)$ $REG3(1:0) = M(9:8)$ $REG4 = O(7:0)$ $REG5(2:0) = O(10:8)$ $Symbol rate f_{symbol_rate} * 2^{32} / f_{clk_ts}$ $Throughout this document, the symbol period is defined as f_{symbol_rate} * 2^{32} / f_{clk_ts}$ $REG74 (LSB) - REG77 (MSB)$ $0 = \text{rectangle (FSK, MSK)}$ $1 = PCM/FM (premod LPF, 3dB cutoff frequency at BT/2)$ $2 = Gaussian (GFSK, GMSK), BT=0.7$ $3 = Gaussian (GFSK, GMSK), BT=0.3$                                                                                                                                                                                               |

| 106M is a multiplier in the range 2.0 to<br>$64.0$ by steps of 1.0. Fixed point<br>format 7.3O is a divider in the range 2.0 to<br>$128.0$ by steps of 1.0. Fixed point<br>format 7.3Note: the graphical use interface<br>computes the best values for M, D<br>and O. $f_{elk\_ts}$ recommended range 80-160<br>MHz.REG1(6:0) = D<br>REG2 = M(7:0)<br>REG3(1:0) = M(9:8)<br>REG4 = O(7:0)<br>REG5(2:0) = O(10:8)Symbol rate<br>fsymbol_ratefsymbol_rateNominal symbol rate, defined as<br>fsymbol_ratefsymbol_rateNore the call of the defined as the time<br>to send one element out of the M-<br>symbol alphabet. In the case of<br>SOQPSK, a symbol represents only<br>one information bit.Premodulation<br>frequency<br>shaping filterPremodulation<br>frequency<br>shaping filterPremodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                          |

| 106M is a multiplier in the range 2.0 to<br>$64.0$ by steps of 1.0. Fixed point<br>format 7.3O is a divider in the range 2.0 to<br>$128.0$ by steps of 1.0. Fixed point<br>format 7.3Note: the graphical use interface<br>computes the best values for M, D<br>and O. $f_{elk\_ts}$ recommended range 80-160<br>MHz.REG1(6:0) = D<br>REG2 = M(7:0)<br>REG3(1:0) = M(9:8)<br>REG4 = O(7:0)<br>REG5(2:0) = O(10:8)Symbol rate<br>fsymbol_ratefsymbol_rateNominal symbol rate, defined as<br>fsymbol_ratefsymbol_rateNore the call of the defined as the time<br>to send one element out of the M-<br>symbol alphabet. In the case of<br>SOQPSK, a symbol represents only<br>one information bit.Premodulation<br>frequency<br>shaping filterPremodulation<br>frequency<br>shaping filterPremodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                          |

| 64.0 by steps of 1.0. Fixed point<br>format 7.3O is a divider in the range 2.0 to<br>128.0 by steps of 1.0. Fixed point<br>format 7.3Note: the graphical use interface<br>computes the best values for M, D<br>and O.fetk_txrecommended range 80-160<br>MHz.REG1(6:0) = D<br>REG2 = M(7:0)<br>REG3(1:0) = M(9:8)<br>REG4 = O(7:0)<br>REG5(2:0) = O(10:8)Symbol rate<br>fsymbol_ratefsymbol_ratefsymbol_ratefsymbol_ratefsymbol_ratefsymbol_ratefsymbol_ratefrequency<br>shaping filterPremodulation<br>frequency<br>shaping filterPremodulation<br>frequency<br>shaping filterREG74 (LSB) - REG77 (MSB)O = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                     |

| 64.0 by steps of 1.0. Fixed point<br>format 7.3O is a divider in the range 2.0 to<br>128.0 by steps of 1.0. Fixed point<br>format 7.3Note: the graphical use interface<br>computes the best values for M, D<br>and O.fetk_txrecommended range 80-160<br>MHz.REG1(6:0) = D<br>REG2 = M(7:0)<br>REG3(1:0) = M(9:8)<br>REG4 = O(7:0)<br>REG5(2:0) = O(10:8)Symbol rate<br>fsymbol_ratefsymbol_ratefsymbol_ratefsymbol_ratefsymbol_ratefsymbol_ratefsymbol_ratefrequency<br>shaping filterPremodulation<br>frequency<br>shaping filterPremodulation<br>frequency<br>shaping filterREG74 (LSB) - REG77 (MSB)O = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                     |

| format 7.3OO is a divider in the range 2.0 to<br>128.0 by steps of 1.0. Fixed point<br>format 7.3Note: the graphical use interface<br>computes the best values for M, D<br>and O. $f_{clk,tx}$ recommended range 80-160<br>MHz.REG1(6:0) = D<br>REG2 = M(7:0)<br>REG3(1:0) = M(9:8)<br>REG4 = O(7:0)<br>REG5(2:0) = O(10:8)Symbol rate<br>f_symbol_ratef_symbol_ratef_symbol_ratef_symbol_rateformationfrequency<br>shaping filterPremodulation<br>frequency<br>shaping filterPremodulation<br>frequency<br>shaping filterPremodulation<br>frequency<br>shaping filterREG74 (LSB) - REG77 (MSB)<br>O = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                         |

| 128.0 by steps of 1.0. Fixed point<br>format 7.3<br>Note: the graphical use interface<br>computes the best values for M, D<br>and O. $f_{clk_tx}$ recommended range 80-160<br>MHz.REG1(6:0) = D<br>REG2 = M(7:0)<br>REG3(1:0) = M(9:8)<br>REG4 = O(7:0)<br>REG5(2:0) = O(10:8)Symbol rate<br>fsymbol_ratefsymbol_rate<br>fsymbol_rateNominal symbol rate, defined as<br>fsymbol_ratefsymbol_rate<br>fsymbol_ratefsymbol_rate<br>fsymbol_rateDef Complexity<br>formation<br>frequency<br>shaping filterPremodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                          |

| 128.0 by steps of 1.0. Fixed point<br>format 7.3<br>Note: the graphical use interface<br>computes the best values for M, D<br>and O. $f_{clk_tx}$ recommended range 80-160<br>MHz.REG1(6:0) = D<br>REG2 = M(7:0)<br>REG3(1:0) = M(9:8)<br>REG4 = O(7:0)<br>REG5(2:0) = O(10:8)Symbol rate<br>fsymbol_ratefsymbol_rate<br>fsymbol_rateNominal symbol rate, defined as<br>fsymbol_ratefsymbol_rate<br>fsymbol_ratefsymbol_rate<br>fsymbol_rateDef Complexity<br>formation<br>frequency<br>shaping filterPremodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                          |

| format 7.3Note: the graphical use interface<br>computes the best values for M, D<br>and O. $f_{clk_tx}$ recommended range 80-160<br>MHz.REG1(6:0) = D<br>REG2 = M(7:0)<br>REG3(1:0) = M(9:8)<br>REG4 = O(7:0)<br>REG5(2:0) = O(10:8)Symbol rate<br>$f_{symbol_rate}$ Nominal symbol rate, defined as<br>$f_{symbol_rate}$ f.ymbol_ratef.ymbol_ratef.geG74 (LSB) - REG77 (MSB)Premodulation<br>frequency<br>shaping filterPremodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| computes the best values for M, D<br>and O. $f_{clk,tx}$ recommended range 80-160<br>MHz.REG1(6:0) = D<br>REG2 = M(7:0)<br>REG3(1:0) = M(9:8)<br>REG4 = O(7:0)<br>REG5(2:0) = O(10:8)Symbol rate<br>f_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symb                                                                                               |

| computes the best values for M, D<br>and O. $f_{clk,tx}$ recommended range 80-160<br>MHz.REG1(6:0) = D<br>REG2 = M(7:0)<br>REG3(1:0) = M(9:8)<br>REG4 = O(7:0)<br>REG5(2:0) = O(10:8)Symbol rate<br>f_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symb                                                                                               |

| and O. $f_{clk\_tx}$ recommended range 80-160<br>MHz.REG1(6:0) = D<br>REG2 = M(7:0)<br>REG3(1:0) = M(9:8)<br>REG4 = O(7:0)<br>REG5(2:0) = O(10:8)Symbol rate<br>f_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_ratef_symbol_rate                                                                                                               |

| MHz.REG1(6:0) = DREG2 = M(7:0)REG3(1:0) = M(9:8)REG4 = O(7:0)REG5(2:0) = O(10:8)Symbol ratefsymbol_ratefsymbol_rateratefsymbol_rateratefsymbol_ratefsymbol_ratefsymbol_ratefsymbol_raterateREG74 (LSB) - REG77 (MSB)Premodulationfrequencyshaping filter0 = rectangle (FSK, MSK)1 = PCM/FM (premod LPF, 3dB)cutoff frequency at BT/2)2 = Gaussian (GFSK,GMSK),BT=0.73 = Gaussian (GFSK,GMSK),BT=0.54 = Gaussian (GFSK,GMSK),BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MHz.REG1(6:0) = DREG2 = M(7:0)REG3(1:0) = M(9:8)REG4 = O(7:0)REG5(2:0) = O(10:8)Symbol ratefsymbol_ratefsymbol_ratefsymbol_ratefsymbol_raterateThroughout this document, the<br>symbol period is defined as the time<br>to send one element out of the M-<br>symbol alphabet. In the case of<br>SOQPSK, a symbol represents only<br>one information bit.Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MHz.REG1(6:0) = DREG2 = M(7:0)REG3(1:0) = M(9:8)REG4 = O(7:0)REG5(2:0) = O(10:8)Symbol ratefsymbol_ratefsymbol_rateratefsymbol_rateratefsymbol_ratefsymbol_ratefsymbol_ratefsymbol_raterateREG74 (LSB) - REG77 (MSB)Premodulationfrequencyshaping filter0 = rectangle (FSK, MSK)1 = PCM/FM (premod LPF, 3dB)cutoff frequency at BT/2)2 = Gaussian (GFSK,GMSK),BT=0.73 = Gaussian (GFSK,GMSK),BT=0.54 = Gaussian (GFSK,GMSK),BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| REG1(6:0) = DREG2 = M(7:0)REG3(1:0) = M(9:8)REG4 = O(7:0)REG5(2:0) = O(10:8)Symbol ratefsymbol_rateNominal symbol rate, defined asfsymbol_ratethroughout this document, the<br>symbol period is defined as the time<br>to send one element out of the M-<br>symbol alphabet. In the case of<br>SOQPSK, a symbol represents only<br>one information bit.Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| REG2 = M(7:0)REG3(1:0) = M(9:8)REG4 = O(7:0)REG5(2:0) = O(10:8)Symbol ratefsymbol_rateNominal symbol rate, defined asfsymbol_rate* $2^{32} / f_{elk_tx}$ Throughout this document, the<br>symbol period is defined as the time<br>to send one element out of the M-<br>symbol alphabet. In the case of<br>SOQPSK, a symbol represents only<br>one information bit.Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| REG2 = M(7:0)REG3(1:0) = M(9:8)REG4 = O(7:0)REG5(2:0) = O(10:8)Symbol ratefsymbol_rateNominal symbol rate, defined asfsymbol_rate* $2^{32} / f_{elk_tx}$ Throughout this document, the<br>symbol period is defined as the time<br>to send one element out of the M-<br>symbol alphabet. In the case of<br>SOQPSK, a symbol represents only<br>one information bit.Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| REG3(1:0) = M(9:8)<br>REG4 = O(7:0)<br>REG5(2:0) = O(10:8)Symbol rate<br>fsymbol_rateNominal symbol rate, defined as<br>fsymbol_rate * $2^{32}$ / felk_txThroughout this document, the<br>symbol period is defined as the time<br>to send one element out of the M-<br>symbol alphabet. In the case of<br>SOQPSK, a symbol represents only<br>one information bit.Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| REG4 = O(7:0)<br>REG5(2:0) = O(10:8)Symbol rate<br>fsymbol_rateNominal symbol rate, defined as<br>fsymbol_rate * $2^{32} / f_{elk\_tx}$ Throughout this document, the<br>symbol period is defined as the time<br>to send one element out of the M-<br>symbol alphabet. In the case of<br>SOQPSK, a symbol represents only<br>one information bit.Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| REG5(2:0) = O(10:8)Symbol rate<br>fsymbol_rateNominal symbol rate, defined as<br>fsymbol_rate * $2^{32}$ / fclk_txThroughout this document, the<br>symbol period is defined as the time<br>to send one element out of the M-<br>symbol alphabet. In the case of<br>SOQPSK, a symbol represents only<br>one information bit.Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Symbol rate<br>$f_{symbol_rate}$ Nominal symbol rate, defined as<br>$f_{symbol_rate} * 2^{32} / f_{clk_tx}$ Throughout this document, the<br>symbol period is defined as the time<br>to send one element out of the M-<br>symbol alphabet. In the case of<br>SOQPSK, a symbol represents only<br>one information bit.Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| f_symbol_ratef_symbol_rate* 2 <sup>32</sup> / f_clk_txThroughout this document, the<br>symbol period is defined as the time<br>to send one element out of the M-<br>symbol alphabet. In the case of<br>SOQPSK, a symbol represents only<br>one information bit.Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Throughout this document, the<br>symbol period is defined as the time<br>to send one element out of the M-<br>symbol alphabet. In the case of<br>SOQPSK, a symbol represents only<br>one information bit.Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| symbol period is defined as the time<br>to send one element out of the M-<br>symbol alphabet. In the case of<br>SOQPSK, a symbol represents only<br>one information bit.Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| symbol period is defined as the time<br>to send one element out of the M-<br>symbol alphabet. In the case of<br>SOQPSK, a symbol represents only<br>one information bit.Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| to send one element out of the M-<br>symbol alphabet. In the case of<br>SOQPSK, a symbol represents only<br>one information bit.Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SOQPSK, a symbol represents only<br>one information bit.REG74 (LSB) – REG77 (MSB)Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| one information bit.REG74 (LSB) – REG77 (MSB)Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| REG74 (LSB) – REG77 (MSB)Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Premodulation<br>frequency<br>shaping filter0 = rectangle (FSK, MSK)<br>1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| frequency<br>shaping filter 1 = PCM/FM (premod LPF, 3dB<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| shaping filter<br>cutoff frequency at BT/2)<br>2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2 = Gaussian (GFSK,GMSK),<br>BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BT=0.7<br>3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3 = Gaussian (GFSK,GMSK),<br>BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BT=0.5<br>4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4 = Gaussian (GFSK,GMSK),<br>BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BT=0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5 = SOQPSK-MIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $(\rho, \mathbf{B}, \mathbf{T}_1, \mathbf{T}_2) = (0, 0, 0.25, 0)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6 = SOQPSK-TG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $(\rho, B, T_1, T_2) = (0.7, 1.25, 1.5, 0.5)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7 = multi-h ARTM CPM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8 = Gaussian (GFSK,GMSK),<br>BT=0.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| REG6(7:4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Spectrum                                                                                                       | Invert Q bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| inversion                                                                                                      | 0 = off, 1 = on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                | REG7(6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Turn output                                                                                                    | Controls the external RF modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| on/off                                                                                                         | through the TX ENB pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                | The TX_ENB control signal to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                | RF modulator will also be turned off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                | when there is no input data to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                | transmit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                | 0 = off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                | 1 = on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                | REG7(7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |