# COM-1826SOFT\_TX TDRSS DSSS Transmitter VHDL source code overview / IP core

## Overview

The COM-1826SOFT\_TX is a NASA/TDRSScompliant Direct Sequence Spread-Spectrum (DSSS) transmitter written in generic VHDL.

The entire **VHDL source code** is deliverable. It is portable to a variety of FPGA targets.

#### Key features and performance:

- TDRSS spread-spectrum digital modulator including

- BPSK and SQPN spread-spectrum modulation

- Programmable 1023- (forward command link) or 2047-chip (return mode 2 link) periodic I and Q Gold codes

- Programmable bit rates from 1 to 150 Kbits/s independent on each channel.

- Convolutional/Viterbi error correction: K=7 Rate <sup>1</sup>/<sub>2</sub>

- NRZ conversion

- Digital baseband I/Q output to external DAC

- 3 types of baseband modulated output waveforms: digital word to DAC, tabdelimited text file, NASA SDDS formatted stream.

- Provided with IP core:

- VHDL source code

- Matlab signal generation .m program for generating baseband waveforms.

- PRBS11 test sequence generator, AWGN noise generator

## Configuration

#### Synthesis-time configuration parameters

The following constants are user-defined in the *COM1826\_TX.vhd* component generic section prior to synthesis. These parameters generally affect the size of the transmitter embodiment.

| Synthesis-time<br>configuration parameters | Configuration                                                                                                                                                                                                           |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AWGN_INST                                  | Additive White Gaussian<br>Noise generator<br>instantiation (1).<br>(0) during operations to<br>save space in FPGA (and<br>to increase clock speed.                                                                     |

| SIMULATION                                 | <ul> <li>(1) to use<br/>COM1826_TX.vhd as its<br/>own testbed, with internal<br/>clock generation.</li> <li>(0) during deployment or<br/>when in use with external<br/>testbeds such as<br/>tbcom1826_tx.vhd</li> </ul> |

# **Run-time configuration parameters**

The user can set and modify the following controls at run-time through the top level component interface:

| Tx Parameters                            | Configuration                                                                                                                                                 |    |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| NRZ1_TX_CONTROL<br>(2:0)                 | Converts NRZ-L to NRZ-<br>L/M/S                                                                                                                               |    |

| NRZ2_TX_CONTROL<br>(2:0)                 | Two converters, for I and Q channels respectively                                                                                                             |    |

|                                          | 000 = NRZ-L unchanged                                                                                                                                         |    |

|                                          | $001 = NRZ-L \text{ to } NRZ_M$                                                                                                                               |    |

|                                          | $010 = NRZ-L \text{ to } NRZ_S$                                                                                                                               |    |

| ENCODER_ENABLED<br>(1:0)                 | Independent<br>convolutional encoder<br>control for each I/Q<br>channels<br>Bit 0: I-channel<br>Bit 1: Q-channel<br>(0) disabled/bypassed,<br>(1) enabled     |    |

| CHIP_RATE<br>(32:0)                      | Chip rate expressed as $2^{32*}$ chip rate / $f_{CLK}$                                                                                                        |    |

|                                          | Chip rate must be strictly less than $f_{CLK}/2$ .                                                                                                            |    |

|                                          | Typically<br>3.077799479166 Mchips/s<br>for TDRSS SMA                                                                                                         |    |

| SYMBOL_RATE1(31:0)<br>SYMBOL_RATE2(31:0) | Two symbol rates, for I<br>and Q channels<br>respectively.<br>Symbol rate expressed as<br>2^32* symbol rate / f <sub>CLK</sub>                                |    |

| LFSRA_INIT(10:0)<br>LFSRC_INIT(10:0)     | Gold code selection as<br>spreading sequence.<br>LFSR initialization. see<br>definition in Space<br>network interoperable pn<br>code libraries, Appendix<br>A |    |

| CODE_MODE                                | 0 = forward command<br>link Gold codes<br>1 = return mode 2 link                                                                                              | CO |

|                                          | Gold codes                                                                                                                                                    |    |

| MOD_SIGNAL_GAIN<br>(15:0)                | Output scaling factor to<br>modulator output<br>(excluding added noise).<br>16-bit unsigned.                                                                  |    |

| NOISE_GAIN(15:0)                         | Additive White Gaussian<br>Noise level (amplitude)<br>for test purposes.<br>Generic parameter<br>AWGN_INST must be '1'.                                       |    |

|                          | 161:0 1                                                                                                                              |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|                          | 16-bit unsigned                                                                                                                      |

| CENTER_FREQ(31:0)        | Modulated signal center<br>frequency. Expressed as<br>$2^{32} * \text{fc}/\text{f}_{\text{CLK}}$                                     |

| MOD_CONTROL(15:0)        | bit 0: spectrum inversion<br>enabled (1) or not (0)                                                                                  |

|                          | bit 1: BPSK (0) vs<br>SQPN(1)                                                                                                        |

|                          | bit 2: dual source (0), or<br>identical data on I/Q (1)                                                                              |

|                          | bit 3: (1) when 1/2 symbol delay added on Q bit                                                                                      |

|                          | bit 4: enable (1)/disable<br>(0) the modulated signal                                                                                |

|                          | bit 5: unused                                                                                                                        |

|                          | bit 6: When enabled, the<br>input data stream is<br>demultiplexed into the I<br>and Q paths. The symbol<br>rate must be identical on |

|                          | both I and Q channels.<br>Two independent FEC<br>encoders are used on the I<br>and Q paths respectively.<br>Enabled(1)/Disabled(0)   |

|                          | bit 7: output spectrum<br>shaping filter (square root<br>raised cosine) bypass (1)<br>or enable (0)                                  |

|                          | bits 9:8: test mode:                                                                                                                 |

|                          | 00 no test,<br>01 = PRBS11,<br>10 = unmodulated carrier                                                                              |

|                          | bit 10: (1) to enable sync<br>word and/or preamble<br>insertion. (0) to disable<br>both.                                             |

|                          | bit 11: spreading<br>enabled(1) / disabled(0)                                                                                        |

|                          | bit 12: differential<br>modulation (1)                                                                                               |

|                          | bits 15:13: unused                                                                                                                   |

| CONFIG_CHANGE_<br>TOGGLE | toggle upon changing the above settings                                                                                              |

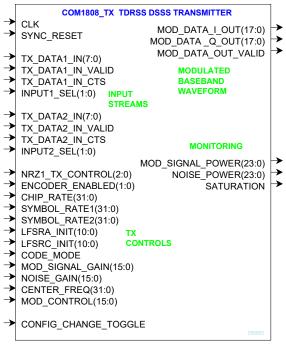

# I/Os

### General

All signals are synchronous with a single input clock CLK\_IN which also serves as DAC sampling clock for the baseband modulated output.

The clock period must be constrained in the constraint file (.xdc for Xilinx Vivado) associated with the project.

This clock must be global clocks (i.e. use BUFG before supplying the clock to the transmitter).

A synchronous reset **SYNC\_RESET** must be supplied. The recommended use is to keep the reset high until the input clock is stable (i.e. PLL or MMCM locked).

### Transmitter

# Data Path

The x indices 1 and 2 refer to the I and Q channels respectively.

**TX\_DATAx\_IN:** 8-bit wide input data for the I(x=1) or Q(x=2) channel respectively. Bit order: MSb first. Read when **TX\_DATAx\_IN\_VALID**= '1'

The user must check the "Clear To Send" flow control signal first before sending the next input Byte.

**TX\_DATAx\_IN\_VALID**:1 CLK-wide input pulses indicating that the associated **TX\_DATAx\_IN** input Byte is valid.

#### TX\_DATAx\_IN\_CTS: output.

Clear-To-Send flow control signal. '1' indicates that the transmitter is ready to accept another input byte. Thanks to an input elastic buffer, the data source is allowed to send a few more bytes after the CTS signal goes low, so timing is generally not critical.

**INPUTx\_SEL(1:0)**: input selection for the I and Q channels.

- 00 = no input

- 01 = user input

- 10 = internally generated PRBS11 test sequence

- 11 = zeros

# Software Licensing

This software is supplied under the following key licensing terms:

- 1. A nonexclusive, nontransferable license to use the VHDL source code internally, and

- 2. An unlimited, royalty-free, nonexclusive transferable license to make and use products incorporating the licensed materials, solely in bit stream format, on a worldwide basis.

The complete VHDL/IP Software License Agreement can be downloaded from http://www.comblock.com/download/softwarelicense.pdf

# Portability

The VHDL source code is written in generic VHDL and thus can be ported FPGAs from various vendors.

# **Configuration Management**

The current software revision is 062025.

| Directory | Contents                                                                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| /doc      | Specifications, user manual, implementation documents                                                                                                  |

| /src      | .vhd source code,.pkg packages, .xdc<br>constraint files (Xilinx)<br>One component per file.                                                           |

| /sim      | VHDL test benches                                                                                                                                      |

| /matlab   | Matlab .m program generating stimulus files<br>for VHDL simulation and for end-to-end<br>BER performance analysis at various signal<br>to noise ratios |

Project files:

Xilinx Vivado v2020 project files: project\_1/project\_1txvivado2020.xpr project\_1/project\_1txvivado2020.tcl

# VHDL development environment

The VHDL software was developed using the following development environment: Xilinx Vivado 2020 for synthesis, place and route and VHDL simulation

# **Device Utilization Summary**

Transmitter device utilization (no AWGN) Device: Xilinx xc7a100tfgg484-1

| Resource | Estimation | Available | Utilization |

|----------|------------|-----------|-------------|

| LUT      | 4258       | 63400     | 6.72        |

| LUTRAM   | 41         | 19000     | 0.22        |

| FF       | 8016       | 126800    | 6.32        |

| BRAM     | 5.50       | 135       | 4.07        |

| DSP      | 12         | 240       | 5.00        |

| ю        | 305        | 285       | 107.02      |

| BUFG     | 1          | 32        | 3.13        |

# Clock and decoding speed

The entire design is synchronous with the CLK\_IN input clock (must be a global clock). A low speed grade Artix7 is sufficient.

Typical maximum clock frequencies for representative FPGA families are listed below:

| Device family                                   | Transmitter |

|-------------------------------------------------|-------------|

| AMD Artix7 100T -1<br>speed grade               | 161 MHz     |

| Xilinx Kintex7<br>ultrascale+ -1 speed<br>grade | 341 MHz     |

### VHDL components overview

### **Top level**

#### COM1826\_TX(Behavioral) (com1826\_tx.vhd) (16)

- TICK1S\_001 : TIMER\_4US(Behavioral) (timer\_4us.vhd)

- LFSR11P\_001 : LFSR11P(behavior) (Ifsr11p.vhd)

- LFSR11P\_002 : LFSR11P(behavior) (Ifsr11p.vhd)

- P8\_TO\_S1\_CONVERSION\_001 : P8\_TO\_S1\_CONVERSION(Behavioral) (p

- P8\_TO\_S1\_CONVERSION\_002 : P8\_TO\_S1\_CONVERSION(Behavioral) (p

- NRZ1\_TX\_001 : NRZ1(Behavioral) (nrz1.vhd)

- NRZ1\_TX\_002 : NRZ1(Behavioral) (nrz1.vhd)

- ENCODER\_ROOT\_1 : ENCODER\_ROOT(behavioral) (encoder\_root.vhd)

- > ENCODER\_ROOT\_2 : ENCODER\_ROOT(behavioral) (encoder\_root.vhd)

- DSSS\_MODULATOR\_001 : DSSS\_MODULATOR\_TDRSS(Behavioral) (ds.

- POWER\_MEASUREMENT\_001 : POWER\_MEASUREMENT(behavior) (pc

- AWGN\_001.AWGN\_001 : AWGN(behavior) (awgn.vhd) (46)

- > AWGN\_001.POWER\_MEASUREMENT\_002b : POWER\_MEASUREMENT(

- > Inst\_SDDS\_TX : SDDS\_tx(Behavioral) (SDDS\_tx.vhd) (2)

- SIM2OUTFILE(Behavioral) (sim2outfile.vhd)

*COM1826\_TX.vhd* is the transmitter top level component. Inputs consist of one or two streams. The output is a complex baseband modulated signal interpolated to one sample per CLK. Internal processing comprises NRZ conversion, convolutional encoding, DSSS modulation and final interpolation.

The input data stream is user-selected among either external input data or internal PRBS-11 pseudo-random test sequence (*LFSR11P.vhd*). The latter is useful in measuring end-to-end tx-rx BER.

The *NRZ1.vhd* component is useful in converting NRZ-M/L/S formats to NRZ-M/L/S.

The *ENCODER\_ROOT.vhd* component performs various convolutional encoding. Two such components can be used for the I and Q channel independently.

*DSSS\_MODULATOR\_TDRSS.vhd* performs the spread-spectrum modulation, root raised cosine filtering, fine frequency translation, level control, and interpolation.

*FIRRCOS20.vhd* is a 20-tap root raised cosine filter operating at 2 samples/chip.

*DIGITAL\_DC2.vhd* implements a digital center frequency translation to fine-tune the output center frequency.

### **Ancillary components**

*LFSR11P.vhd* is a pseudo-random sequence generator used for test purposes. It generates a PRBS11 test sequence commonly used for bit error rate testing at the receiving end of a transmission channel.

*AWGN.vhd* generates a precise Additive White Gaussian Noise. The noise bandwidth is 2\*symbol rate.

*BRAM\_DP2.vhd* is a generic dual-port memory, used as input and output elastic buffers. Memory is inferred (no Xilinx primitive is used).

SIM2OUTFILE.vhd writes modulated output waveform to a tab-delimited file (com1826\_tx.txt) which can be subsequently read by Matlab (load command) for plotting or analysis. This output file can also be used as input waveform for the receiver testbench tbcom1826\_rx.vhd. Set SIMULATION to '1' to enable this feature.

Alternatively, the modulated output waveform can be formatted as NASA/SDDS on an Ethernet LAN using the sdds tx.vhd component.

### VHDL simulation

VHDL testbenches are located in the /sim directory.

The tbcom1826\_tx.vhd sends two PRBS-11 test sequences through the transmitter . The output consists of modulated complex baseband samples. It generates the clock, reset and configures the transmitter for chip rate, symbol rates, NRZ conversion, spreading code selection, transmit level, center frequency, etc.

# Matlab simulation

The siggen\_tdrss.m is a matlab program to generate a TDRSS spread-spectrum modulation waveform, saved into a file which can serve as a stimulus input to a receiver. It is functionally equivalent to the tbcom1826\_tx.vhd VHDL testbed.

### **Reference documents**

[1] ] Space Network Users Guide; Rev 10

### Acronyms

| Acrony<br>m | Definition                      |

|-------------|---------------------------------|

| AWGN        | Additive White Gaussian Noise   |

|             |                                 |

| CTS         | Clear-To-Send flow control flag |

| DAS         | Demand Access System            |

| DSSS        | Direct Sequence Spread          |

|             | Spectrum (modulation)           |

| FPGA        | Field Programmable Gate Array   |

| GbE         | Gigabit Ethernet                |

| LFSR        | Linear Feedback Shift Register  |

| LSb         | Least Significant bit in a word |

| MSb         | Most Significant bit in a word  |

| RF          | Radio Frequency                 |

| rx          | Receive                         |

| SDDS        | Signal Data Distribution        |

|             | Standard                        |

| SQPN        | Staggered Quadriphase PN        |

|             | (spread-spectrum modulation)    |

| SRRC        | Square Root Raised Cosine       |

|             | (filter)                        |

| TDRSS       | Tracking and Data Relay         |

|             | Satellite System                |

| tx          | Transmit                        |

## **ComBlock Ordering Information**

COM-1826SOFT\_TX TDRSS DSSS transmitter, VHDL source code / IP core

ECCN: EAR99

## **Contact Information**

MSS • 845-N Quince Orchard Boulevard • Gaithersburg, Maryland 20878-1676 • U.S.A. Telephone: (240) 631-1111 E-mail: info@comblock.com