# COM-1209ASOFT HIGH-SPEED DVB-S2 BCH CODE DECODER & ENCODER VHDL SOURCE CODE OVERVIEW

### Overview

- High-speed BCH block code encoder and decoder for FPGAs. Also includes BER tester and PRBS11 test sequence generator.

- Fully compliant with the DVB-S2 standard ETSI EN 302 307

- Parallel I/Os and processing for high-speed operation:

- 2.7 Gbits/s encoding [Xilinx Ultrascale+]

- up to 1.7 Gbits/s decoding [Xilinx Ultrascale+]]

- Corrects t = 8, 10 or 12 errors per block.

- Decoder flags frames with uncorrectable errors.

- Decoder reports number of bit errors corrected at the end of each decoded block.

# Portable VHDL code

The code is written in generic standard VHDL and is thus portable to a variety of FPGAs. The code was developed and tested on a Xilinx 7-series FPGA but is expected to work similarly on other targets. No manufacturer-specific primitive is used.

#### Encoder

#### l/Os

8-bit parallel data input and output help maximize the throughput. The first byte in the stream is marked by a Start Of Frame (SOF) flag.

Flow control is ensured through the SAMPLE\_CLK\_x\_REQ signals which convey "Clear To Send" information from the stream recipient. The data source must immediately stop sending data when the data sink clears this signal.

All inputs and outputs are synchronous with the rising edge of the synchronous clock CLK.

#### Speed

| FPGA                     | Clock<br>(max) | Encoder<br>output<br>data rate |

|--------------------------|----------------|--------------------------------|

|                          |                | (max)                          |

| Xilinx Zynq Ultrascale+  | 357 MHz        | 2.7 Gbits/s                    |

| -1 (slowest) speed grade |                |                                |

| Xilinx Artix7            | 198 MHz        | 1.5 Gbits/s                    |

| -1 (slowest) speed grade |                |                                |

| Xilinx Virtex-5          | 131 MHz        | 1 Gbits/s                      |

| Xilinx Spartan-3         | 83 MHz         | 650 Mbits/s                    |

A minimum guard time of at least  $(N_{bch} - K_{bch})/8 + 2$ clocks must be inserted between successive input frames to let the encoder send the parity bits to its

MSS • 845-N Quince Orchard Boulevard • Gaithersburg, Maryland 20878 • U.S.A. Telephone: (240) 631-1111 www.ComBlock.com © MSS 2023 Issued 6/27/2023 output. More generally, the data source should check the flow control signal SAMPLE\_CLK\_IN\_REQ before sending any input data to the encoder.

#### **Device Utilization Summary**

Device: Xilinx Artix7

| Flip Flops | 262 |

|------------|-----|

| LUTs       | 620 |

| 36Kb BRAM  | 0   |

| DSP        | 0   |

| GCLKs      | 1   |

## Decoder

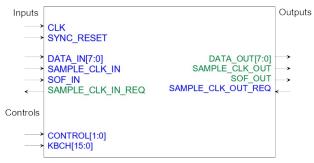

#### I/Os

| Inputs        |                                                              |                                                                             | Outputs                                                                                |

|---------------|--------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| $\rightarrow$ | CLK<br>SYNC_RESET                                            |                                                                             |                                                                                        |

|               | DATA_IN[7:0]<br>SAMPLE_CLK_IN<br>SOF_IN<br>SAMPLE_CLK_IN_REQ | DATA_OUT[7:0]<br>SAMPLE_CLK_OUT<br>SOF_OUT<br>EOF_OUT<br>SAMPLE_CLK_OUT_REQ | $ \xrightarrow{\rightarrow} \\ \xrightarrow{\rightarrow} \\ \xrightarrow{\leftarrow} $ |

| Controls      |                                                              |                                                                             | Monitoring                                                                             |

|               | CONTROL[1:0]<br>NBCH[15:0]<br>KBCH[15:0]                     | N_CORRECTED[3:0]<br>GOOD_FRAME                                              | $\rightarrow$                                                                          |

#### Speed

| -                         | -       |                         |

|---------------------------|---------|-------------------------|

| FPGA                      | Clock   | Decoder input data rate |

|                           | (max)   | (max)                   |

| Xilinx Zynq               | 294 MHz | 1.43 Gbits/s            |

| Ultrascale+               |         | (51840,51648,12)        |

| -1(slowest)               |         |                         |

| speed grade               |         | 1.7 Gbits/s             |

|                           |         | (58320,58192,8)         |

| Xilinx                    | 166 MHz | 810 Mbits/s             |

| Virtex-5                  |         | (51840,51648,12)        |

|                           |         | 963 Mbits/s             |

|                           |         | (58320,58192,8)         |

| Xilinx                    | 153 MHz | 746 Mbits/s             |

| Artix7 -                  |         | (51840,51648,12)        |

| 1(slowest)<br>speed grade |         | 886 Mbits/s             |

|                           |         | (58320,58192,8)         |

| Xilinx                    | 73 MHz  | 356 Mbits/s             |

| Spartan-3                 |         | (51840,51648,12)        |

|                           |         | 423 Mbits/s             |

|                           |         | (58320,58192,8)         |

|                           |         |                         |

The decoder architecture is such that the three decoding stages are pipelined and the input data is stored in a 128 Kbits elastic buffer until the error locations are found. Therefore, it is possible to input a new frame even before the previous one is completely decoded.

The processing time budget for each decoding stage can be expressed as follows:

1. syndrome computation: 16.5 \* t clocks.

- 2. error location polynomial: 328 \* t clocks in the worst case, when t errors are present in the received frame.

- factoring the error location polynomial before the first output byte: (2<sup>16</sup> – N<sub>bch</sub>)/8 + 4 clocks for GF(2<sup>16</sup>)

- 4. Output:  $K_{bch}/8$  clocks

Using the above information, one can compute the maximum decoding speed for each DVB-S2 BCH code variant. For example, the best decoding speed for the (51840,51648,12) code is 51840/8 + (16.5 + 328)\*12 = 10614 clocks per frame.

#### **Device Utilization Summary**

Device: Xilinx Artix7

| Flip Flops | 5395 |

|------------|------|

| LUTs       | 5442 |

| 36Kb BRAM  | 4.5  |

| DSP        | 0    |

| GCLKs      | 1    |

#### **DVB-S2 BCH**

The DVB-S2 standard lists includes 21 variants of long BCH codes. Each variant is identified by its code block size  $N_{bch}$ , uncoded block size  $K_{bch}$ , error correction capability t and frame type.

The VHDL code implements all 21 variants listed in tables 5a and 5b of the specifications [1].

| Kbch  | N <sub>bch</sub> | t  | Frame  |

|-------|------------------|----|--------|

| 16008 | 16200            | 12 | normal |

| 51648 | 51840            | 12 | normal |

| 53840 | 54000            | 10 | normal |

| 58192 | 58320            | 8  | Normal |

| 3072  | 3240             | 12 | short  |

The codes for normal frames are computed in  $GF(2^{16})$ , whereas the short frame codes are computed over  $GF(2^{14})$ .

The primitive polynomials used to generate the Galois fields are  $x^{16} + x^5 + x^3 + x^2 + 1$  for GF(2<sup>16</sup>) and  $x^{14} + x^5 + x^3 + x + 1$  for GF(2<sup>14</sup>)

Matlab: Primpoly(16,'min') Primpoly(14,'min')

The specification document lists the 12 minimum polynomials  $g_i(x)$  for  $GF(2^{16})$  and  $GF(2^{14})$  in tables 6a and 6b respectively.

By multiplying the first 8, 10 or 12 minimum polynomials, we can construct the generator polynomials for four configurations:  $GF(2^{16})$  t=8,10,12 and  $GF(2^{14})$  t=12.

The resulting generator polynomials can be represented by their binary coefficients as listed below:

```

constant GENPOLY0:

std_logic_vector(128 downto 0) :=

"1" & x"1c07255f712797bd19fc6d7504f9662B";

constant GENPOLY1:

std_logic_vector(160 downto 0) :=

"1" &

"60150CEDFC2A331F6A785703EFD12301B8BB6591"

;

constant GENPOLY2:

std_logic_vector(192 downto 0) := "1" &

```

```

x"4E260E83845C511C50CF2CD8DC350889034785F7

660255E7";

```

```

constant GENPOLY3:

std_logic_vector(168 downto 0) := "1" &

x"4062DBEA9869B262CD23A39069528FE7D7D11905

A5";

```

The encoder uses these generator polynominals to generate the  $(N_{bch} - K_{bch})$  parity bits appended to the K<sub>bch</sub> input data bits. As described in section 5.3.1 of the DVB-S2 specifications [1], the parity bits are the remainder of a polynomial division of the shifted input bits by the generator polynomial.

#### **DVB-S2 BCH Decoding**

Decoding a BCH block is done in three steps.

- 1. compute the syndromes

- 2. derive the error location polynominal

- 3. find the roots of the error location polynominal and correct the bit errors.

#### Syndromes

To compute a syndrome  $S_i$ , one must first divide the input block by the twelve polynomials  $g_j(x)$ , where  $g_j(x)$  represent the minimum polynomials of  $\alpha^i$  for i = 1 to 2t (see table below). The twelve minimum polynomials  $g_j(x)$  are listed in the DVB-S2 specifications in Tables 6a and 6b.

The remainder  $b_j(x)$  is then evaluated for  $\alpha^i$  as  $S_i = b_j(\alpha^i)$ .

| Minimum polynomial $g_j(x)$ | Roots $\alpha^i$                                             |

|-----------------------------|--------------------------------------------------------------|

| $g_1(x)$                    | $\alpha^{,} \alpha^{2,} \alpha^{4,} \alpha^{8,} \alpha^{16}$ |

| $g_2(x)$                    | $\alpha^{3}$ , $\alpha^{6}$ , $\alpha^{12}$ , $\alpha^{24}$  |

| g <sub>3</sub> (x)          | $\alpha^{5,}\alpha^{10,}\alpha^{20}$                         |

| g <sub>4</sub> (x)          | $\alpha^{7,} \alpha^{14}$                                    |

| g <sub>5</sub> (x)          | $\alpha^{9}, \alpha^{18}$                                    |

| g <sub>6</sub> (x)          | $\alpha^{11}, \alpha^{22}$                                   |

| g <sub>7</sub> (x)          | $\alpha^{13}$                                                |

| $g_8(x)$                    | $\alpha^{15}$                                                |

| g <sub>9</sub> (x)          | $\alpha^{17}$                                                |

| g <sub>10</sub> (x)         | $\alpha^{19}$                                                |

| $g_{11}(x)$                 | $\alpha^{21}$                                                |

| $g_{12}(x)$                 | $\alpha^{23}$                                                |

The roots of  $g_j(x)$  are as follows:

When a received frame is error-free, all syndromes are zero.

Verifying the syndrome computation is easy. Assumming two bit errors at locations 16191 and 16184 (with bit locations being numbered from  $N_{bch}$ -1 (first bit received) to 0), then  $S_1 = \alpha^{16191} + \alpha^{16184}$   $S_2 = (\alpha^{16191})^2 + (\alpha^{16184})^2$   $S_3 = (\alpha^{16191})^3 + (\alpha^{16184})^3$ ...  $S_{2t} = (\alpha^{16191})^{2t} + (\alpha^{16184})^{2t}$

Matlab: prim\_poly16 = primpoly(16, 'min'); alpha = gf(2,16, prim\_poly16); s1 = alpha^16191 + alpha^16184; s2 = (alpha^16191)^2 + (alpha^16184)^2 s3 = (alpha^16191)^3 + (alpha^16184)^3 ... s24 = (alpha^16191)^24 + (alpha^16184)^24

#### **Error Location Polynomial**

The Berlekamp-Massey algorithm is implemented to find the error location polynomial.  $\sigma(x) = (1+\alpha^{L1}x) (1+\alpha^{L2}x) (1+\alpha^{L3}x) (1+\alpha^{L4}x)...$ where Li are the error locations. At the end of this step, the error location polynomial is expressed as  $\sigma(x) = \sigma_0 + \sigma_1 x + \sigma_2 x^2 + \sigma_3 x^3 + ...$

Comparing the VHDL simulation with Matlab is easy. Let us assume two bit errors at locations 16191 and 16184 (with bit locations being numbered from N<sub>bch</sub>-1 (first bit received) to 0), then the error location polynomial is computed by expanding  $(1+\alpha^{16191}x) (1+\alpha^{16184}x)$

```

Matlab:

prim_poly16 = primpoly(16, 'min');

alpha = gf(2,16, prim_poly16);

p1 = [alpha^16191 1];

p2 = [alpha^16184 1];

elp = conv(p1,p2);

```

## **Factoring and Error Correction**

Chien's search circuit [3] is used to factor the error location polynomial  $\sigma(x)$ . While the data bit at location Li is streamed to the output, the algorithm assesses whether  $\alpha^{-Li}$  is a root of  $\sigma(x)$ . If so, it is erroneous and is corrected.

128Kbits of block RAM is used as elastic buffer to temporarily store the received bits while error decoding takes place.

### Reference documents

[1] ETSI EN 302 307, Section 5.3 FEC encoding

[2] "Shift-Register Synthesis and BCH Decoding", James L. Massey, IEEE Transactions on Information Theory, January 1969.

[3] "Error Control Coding, Fundamentals and Applications", Shu Lin / Daniel Costello.

### **Flow Control**

The decoder input first goes through an input elastic buffer to regulate the flow. The buffer output data flow is sent to two components: the syndrome computation *bch\_syndromes.vhd* and the error correction *bch\_ec.vhd*. Thus, both components are able to control the data flow from the input elastic buffer using their flow control signals SAMPLE0A CLK REQ and SAMPLE0B CLK REQ respectively.

Syndromes computation is performed on the fly. Upon reading the last frame byte from the input elastic buffer, *bch\_syndromes.vhd* exercises its SAMPLE0A\_CLK\_REQ flow control signal to immediately stop the input flow before a new start of frame. The end of syndromes computation is marked by the availability of the syndromes (SYNDROME1 through 24) and a pulse SYNDROME\_SAMPLE\_CLK. At this point *bch\_syndromes.vhd* is ready for the next input frame.

The syndromes are passed to *bcherrorlocator.vhd* to compute the error location polynomials. The computation is triggered by the SYNDROME\_SAMPLE\_CLK pulse and ends at the ELP\_CLK pulse. The resulting error location polynomials are available in ELP1 through 12. In the special case of an error-free frame, there is no need to compute the error location polynomials. The ALL\_ZERO\_SYNDROMES net goes high when this happens.

The final decoding step, error correction, is implemented within the *bch\_ec.vhd* component. This component includes a 128 Kbit elastic buffer large enough receive a new frame while processing the previous one. The purpose of the SAMPLEOB\_CLK\_REQ flow control flag is stop the input data flow unless at least 1/32th of the internal elastic buffer is available.

| Signal               | Valu | 250000ns                              | 300000ns :                              | 350000ns | 400000ns 450000ns                     | 500000ns 5 | 50000ns | 600000ns                                | 650000n                                             | s 700000ns                              | 750000n                                 |

|----------------------|------|---------------------------------------|-----------------------------------------|----------|---------------------------------------|------------|---------|-----------------------------------------|-----------------------------------------------------|-----------------------------------------|-----------------------------------------|

| DATA_IN              | 00   | 00 46                                 | 0( (                                    | i        | BE                                    |            | I       | (                                       | 1                                                   | 1                                       | ٤                                       |

| SAMPLE_CLK_IN        | '0'  |                                       | · · • • • • • • • • • • • • • • • • • • |          | · · · · · · · · · · · · · · · · · · · |            |         | • • • • • • • • • • • • • • • • • • • • | ••••                                                | •••••                                   | ••••••••••••••••••••••••••••••••••••••• |

| SAMPLE_CLK_IN_REQ    | '0'  |                                       |                                         |          |                                       |            |         | ••••                                    | •••••                                               |                                         |                                         |

| SOF_IN               | '0'  |                                       |                                         |          |                                       |            |         |                                         | · · · · <mark>· · · · · · · · · · · · · · · </mark> |                                         |                                         |

| DATAO                | 4F   | 4F                                    | C 1                                     | E        | 33                                    |            | 1       | i                                       | i                                                   | 1                                       |                                         |

| SAMPLEO_CLK          | '0'  |                                       | · · • • • • • • • • • • • • • • • • •   |          | ·····                                 |            |         |                                         |                                                     | ••••                                    | •••••••••••                             |

| SAMPLEO_CLK_REQ      | '0'  |                                       |                                         |          |                                       |            |         | ••••                                    | • • • • • • • • • • •                               |                                         | ••••••••••                              |

| SAMPLEOA_CLK_REQ     | '1'  |                                       |                                         |          |                                       |            |         | ••••                                    |                                                     | • • • • • • • • • • • • • • • • • • • • | •••••••                                 |

| SAMPLEOB_CLK_REQ     | 101  |                                       |                                         |          |                                       |            |         | • • • • • • • • • • •                   |                                                     |                                         |                                         |

| SOFO                 | 101  | · · · · · · · · · · · · · · · · · · · | · · · <b>·</b> · · · · · · · · · · ·    |          |                                       |            |         |                                         |                                                     |                                         |                                         |

| SYNDROME_SAMPLE_CLK  | 101  |                                       |                                         | ·····    |                                       |            |         |                                         |                                                     | <mark>.</mark>                          | <mark></mark>                           |

| SYNDROME_SAMPLE_CLKB | 101  |                                       |                                         |          |                                       |            |         |                                         |                                                     |                                         |                                         |

| SYNDROME1            | 30F7 | 30F7                                  | 0000                                    |          | FC8C                                  |            |         |                                         |                                                     |                                         | 0000                                    |

| ALL_ZERO_SYNDROMES   | 101  |                                       |                                         |          |                                       |            |         |                                         |                                                     |                                         |                                         |

| DATA_OUT             | x    | x                                     | 3                                       |          | 3 E                                   |            | 5       | 2                                       | 8                                                   | 3                                       | 1                                       |

| SAMPLE_CLK_OUT       | '0'  |                                       |                                         |          |                                       |            |         | • • • • • • • • • •                     |                                                     |                                         | •••••••                                 |

| SAMPLE_CLK_OUT_REQ   | ' 1' |                                       |                                         |          |                                       |            |         |                                         |                                                     |                                         |                                         |

| SOF_OUT              | '0'  | · · · · · · · · · · · · · · · · · · · | <u></u>                                 |          |                                       |            |         |                                         |                                                     |                                         | <mark>.</mark>                          |

| EOF_OUT              | '0'  |                                       |                                         |          |                                       |            |         |                                         |                                                     |                                         |                                         |

| CLK                  | 101  |                                       |                                         |          |                                       |            |         |                                         |                                                     |                                         |                                         |

| CONTROL              | 2    |                                       |                                         |          |                                       |            | 2       |                                         |                                                     |                                         |                                         |

| ELP1                 | 30F7 | 30F7                                  |                                         | 0        |                                       |            |         | F                                       | C8C                                                 |                                         |                                         |

| ELP12                | 36B6 | 36B6                                  |                                         |          |                                       |            |         | 00                                      | 000                                                 |                                         |                                         |

| ELP_CLK              | 101  |                                       |                                         |          |                                       |            |         |                                         |                                                     |                                         |                                         |

| КВСН                 | 3E88 |                                       |                                         |          |                                       |            | 3E88    |                                         |                                                     |                                         |                                         |

| NBCH                 | 3F48 |                                       |                                         |          |                                       |            | 3F48    |                                         |                                                     |                                         |                                         |

| GOOD_FRAME           | '0'  |                                       | [ ]                                     |          |                                       |            |         |                                         |                                                     |                                         |                                         |

| N_CORRECTED          | 0    |                                       |                                         | 0        |                                       |            | 6       |                                         | 0                                                   | _                                       | 6                                       |

| N_CORRECTED          |      |                                       |                                         |          |                                       |            |         |                                         |                                                     |                                         |                                         |

*Typical bch\_dec.vhd capture. Includes input frames with correctable and uncorrectable errors.*

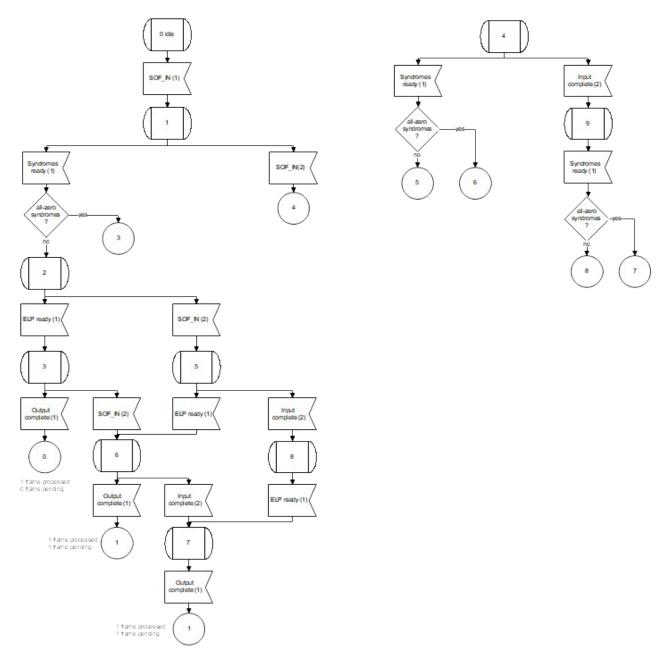

The flow control is primarily located within *bch\_ec.vhd*. It is a little bit complex. There are five key events in the life of a BCH frame decoding, in the order of occurrence:

- input start of frame pulse SOF\_IN

- received all input data (excluding parity bits) INPUT\_DATA\_COMPLETE

- syndrome ready pulse SYNDROME\_SAMPLE\_CLK

- error location ready pulse ELP\_CLK\_IN

- all decoded bytes sent out OUTPUT\_DATA\_COMPLETE

Note: the error location computation is skipped if ALL\_ZERO\_SYNDROMES is high.

| Signal               | Value | 250000ns                              | 300000ns                                 | 350000ns                                | 400000ns 450000ns | 500000ns 5                            | 50000n | s ( | 500000ns | 650000ns                           | 700000ns                                            | 750            |

|----------------------|-------|---------------------------------------|------------------------------------------|-----------------------------------------|-------------------|---------------------------------------|--------|-----|----------|------------------------------------|-----------------------------------------------------|----------------|

| DATA_IN              | во    | 4F                                    | C                                        | ٤                                       | 33                |                                       | r      |     | i        | i                                  | 4                                                   |                |

| SAMPLE_CLK_IN        | 111   |                                       |                                          |                                         |                   |                                       |        |     |          |                                    | • • • • • • • • • • • • • •                         | •••••          |

| SAMPLE_CLK_IN_ENABLE | '1'   |                                       |                                          |                                         |                   |                                       |        |     |          |                                    | ••••                                                | • • • • • • •  |

| AMPLE_CLK_IN_REQ     | ' 1 ' |                                       |                                          |                                         |                   |                                       |        |     |          | •••                                |                                                     |                |

| SAMPLE_CLK_INB       | 11    |                                       |                                          | •                                       |                   |                                       |        |     | ]        |                                    | · · · · · · · · · · · · ·                           |                |

| SOF_IN               | 'O'   |                                       |                                          |                                         |                   |                                       |        |     |          |                                    |                                                     |                |

| INPUT_BYTE_COUNTER   | 0171  | 07D1                                  |                                          | C                                       | 07D1              |                                       |        |     | C        | C                                  | C                                                   | C              |

| КВСН                 | 3E88  |                                       |                                          |                                         |                   |                                       | 3E88   |     |          |                                    |                                                     |                |

| YNDROME_SAMPLE_CLK   | 101   |                                       |                                          |                                         |                   |                                       |        |     |          |                                    |                                                     |                |

| LP_CLK_IN            | 101   |                                       |                                          |                                         |                   |                                       |        |     |          |                                    |                                                     |                |

| ALL_ZERO_SYNDROMES   | 111   |                                       |                                          |                                         | •••••••           |                                       |        |     |          |                                    |                                                     |                |

| WPTR                 | 2F0F  | OFD2                                  |                                          | 1                                       | 1F74              |                                       |        |     | 2        | 2                                  | 3                                                   | 3              |

| RPTR                 | 270D  | 3FFF                                  | C                                        |                                         | OFA1              |                                       | 1      |     | 1        | 2                                  | 2                                                   | 3              |

| BUFSIZE              | 0801  | OFD2                                  | 0801                                     |                                         | OFD2              |                                       |        |     |          |                                    | C                                                   | 801            |

| STATE                | 3     | 1 2                                   | C 3                                      | 0                                       | 1                 | 2                                     | C      | 3   | C 3      | C 3                                | C 3                                                 | ( 3            |

| C_STATE              | 6     | 7                                     | 16                                       | 1 5                                     | ۶ 7               |                                       | 1      | 6   | 1 6      | 16                                 | 16                                                  | : 6            |

| INPUT_DATA_COMPLETE  | '0'   |                                       | ••••                                     | <u> </u>                                |                   |                                       | •••••• |     | <u>Π</u> | <u></u>                            |                                                     | ·····          |

| OUTPUT_DATA_COMPLETE | '0'   |                                       |                                          |                                         |                   |                                       |        |     |          |                                    | · · · <mark>· · · · · · · · · · · · · · · · </mark> |                |

| SAMPLE_CLK_IN_REQB   | '1'   |                                       |                                          | ••••••••••••••••••••••••••••••••••••••• |                   |                                       |        |     |          | • • • • • • • • • • •              | •••                                                 |                |

| data_out             | x     | x                                     | 7                                        |                                         | 3E                |                                       | 5      |     | 9        | ٤                                  | 8                                                   | 1              |

| SAMPLE_CLK_OUT       | '1'   | · · · · · · · · · · · · · · · · · · · | ••••••••••                               | •                                       |                   | · · · · · · · · · · · · · · · · · · · |        |     | 1        | •••••                              |                                                     |                |

| SAMPLE_CLK_OUT_LOCAL | 111   |                                       |                                          | • • • • • • • • • • • • •               |                   |                                       |        |     |          | · · · <mark>·</mark> · · · · · · · | · · · · · · · · · · · · · · · · · · ·               | •••••          |

| SAMPLE_CLK_OUT_REQ   | '1'   |                                       |                                          |                                         |                   |                                       |        |     |          |                                    |                                                     |                |

| SOF_OUT              | '0'   | · · · · · · · · · · · · · · · · · · · | · · · <mark>·</mark> · · · · · · · ·     |                                         |                   |                                       |        |     |          |                                    | ••••                                                | <mark>.</mark> |

| EOF_OUT              | '0'   |                                       |                                          | · · · · · · · · · · · · · ·             |                   |                                       |        |     |          |                                    |                                                     |                |

| ERROR_CORRECTION     | 00    |                                       |                                          | 00                                      |                   |                                       |        |     | C        | 0                                  |                                                     |                |

| GOOD_FRAME           | 111   |                                       |                                          | •••••••••••••                           |                   |                                       |        |     |          |                                    | ••••••••••                                          |                |

| _CORRECTED           | x     |                                       |                                          | 0                                       |                   |                                       | 6      |     |          | 0                                  |                                                     | 6              |

| IEA1                 | '0'   |                                       |                                          |                                         |                   |                                       |        |     |          |                                    |                                                     |                |

| EA2                  | '0'   |                                       | · · · · <mark> </mark> · · · · · · · · · |                                         |                   |                                       |        |     |          |                                    |                                                     |                |

| JE A 3               | 101   |                                       |                                          |                                         |                   |                                       |        |     |          |                                    |                                                     |                |

*Typical bch\_ec.vhd capture. Includes frames with correctable and uncorrectable errors.*

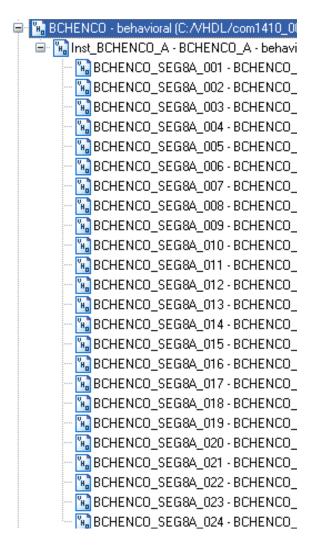

### VHDL software hierarchy

The code is stored with one, and only one, entity per file.

## Encoder

#### Decoder

The decoder hierarchical structure reflects the three successive decoding steps:

- 1. *bch\_syndromes.vhd*: compute the syndromes

- 2. *bcherrorlocator.vhd*: derive the error location polynominal

- 3. *bch\_ec.vhd*: find the roots of the error location polynominal and correct the bit errors.

#### 😑 😘 💑 BCH\_DEC - behavioral (C:/VHDL/com1410\_000/src/b

- 🖶 🔚 Inst\_BCH\_SYNDROMES BCH\_SYNDROMES beha

- 🖶 强 Inst\_BCHERRORLOCATOR BCHERRORLOCATOR

- 🖮 🔚 BCH\_EC\_001 BCH\_EC behavioral (C:/VHDL/com1-

## Clock / Timing

The software uses a single master clock (CLK) which serves as input clock, output clock and signal processing clock.

## **Test Benches**

Several test benches are included for end-to-end and component-level VHDL simulation:

• /*sim/tbbchencdec2.vhd*: end-to-end simulation including encoder, decoder and added bit errors.

## Software Licensing

The COM-1209ASOFT is supplied under the following key licensing terms:

- 1. A nonexclusive, nontransferable license to use the VHDL source code internally, and

- 2. An unlimited, royalty-free, nonexclusive transferable license to make and use products incorporating the licensed materials, solely in bit stream format, on a worldwide basis.

The complete VHDL/IP Software License Agreement can be downloaded from http://www.comblock.com/download/softwarelicense.pdf

# **Configuration Management**

The current software revision is 5b.

| Directory | Contents                                                                                                                                                                                                        |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /doc      | Specifications, user manual, implementation documents                                                                                                                                                           |

| /src      | .vhd source code,.pkg packages, .xdc<br>constraint files (Xilinx)<br>One component per file.                                                                                                                    |

| /sim      | VHDL test benches                                                                                                                                                                                               |

| /matlab   | Matlab .m file for simulating the encoding<br>and decoding algorithms, for generating<br>stimulus files for VHDL simulation and for<br>end-to-end BER performance analysis at<br>various signal to noise ratios |

Project files:

Xilinx Vivado v2020 project file: project\_1v2020.xpr tcl: project\_1\_v2020.tcl

### VHDL development environment

The VHDL software was developed using the following development environment:

(a) Xilinx Vivado 2020 for synthesis, place and route and VHDL simulation

## **ComBlock Ordering Information**

COM-1209ASOFT High-speed DVB-S2 BCH encoder & decoder. VHDL source code IP core

ECCN: EAR99

## **Contact Information**

MSS • 845-N Quince Orchard Boulevard • Gaithersburg, Maryland 20878-1676 • U.S.A. Telephone: (240) 631-1111 E-mail: info@comblock.com